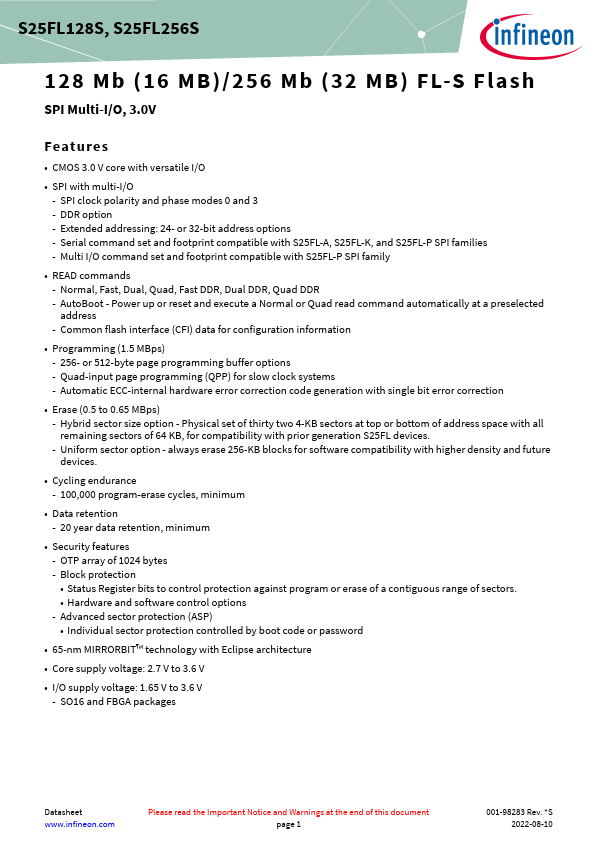

S25FL128S

Overview

- CMOS 3.0 V core with versatile I/O

- SPI with multi-I/O - SPI clock polarity and phase modes 0 and 3 - DDR option - Extended addressing: 24- or 32-bit address options - Serial command set and footprint compatible with S25FL-A, S25FL-K, and S25FL-P SPI families - Multi I/O command set and footprint compatible with S25FL-P SPI family

- READ commands - Normal, Fast, Dual, Quad, Fast DDR, Dual DDR, Quad DDR - AutoBoot - Power up or reset and execute a Normal or Quad read command automatically at a preselected address - Common flash interface (CFI) data for configuration information

- Programming (1.5 MBps) - 256- or 512-byte page programming buffer options - Quad-input page programming (QPP) for slow clock systems - Automatic ECC-internal hardware error correction code generation with single bit error correction

- Erase (0.5 to 0.65 MBps) - Hybrid sector size option - Physical set of thirty two 4-KB sectors at top or bottom of address space with all remaining sectors of 64 KB, for compatibility with prior generation S25FL devices. - Uniform sector option - always erase 256-KB blocks for software compatibility with higher density and future devices.

- Cycling endurance - 100,000 program-erase cycles, minimum

- Data retention - 20 year data retention, minimum

- Security features - OTP array of 1024 bytes - Block protection

- Status Register bits to control protection against program or erase of a contiguous range of sectors.

- Hardware and software control options - Advanced sector protection (ASP)