IS41LV8512

IS41LV8512 is 512K x 8 DYNAMIC RAM manufactured by Integrated Circuit Solution.

- Part of the IS41C8512 comparator family.

- Part of the IS41C8512 comparator family.

IS41C8512 IS41LV8512

.EATURES

..

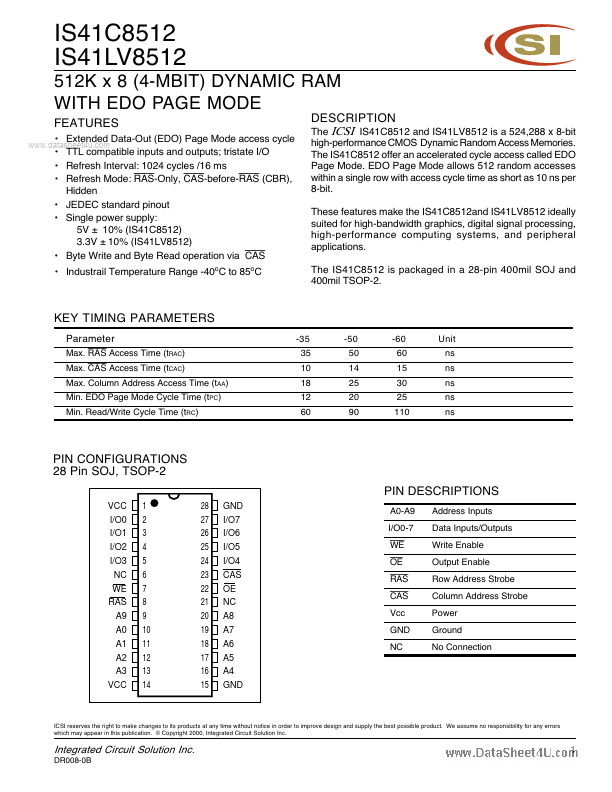

512K x 8 (4-MBIT) DYNAMIC RAM WITH EDO PAGE MODE

Extended Data-Out (EDO) Page Mode access cycle TTL patible inputs and outputs; tristate I/O Refresh Interval: 1024 cycles /16 ms Refresh Mode: RAS-Only, CAS-before-RAS (CBR), Hidden JEDEC standard pinout Single power supply: 5V ± 10% (IS41C8512) 3.3V ± 10% (IS41LV8512) Byte Write and Byte Read operation via CAS Industrail Temperature Range -40o C to 85o C

DESCRIPTION The 1+51 IS41C8512 and IS41LV8512 is a 524,288 x 8-bit high-performance CMOS Dynamic Random Access Memories. The IS41C8512 offer an accelerated cycle access called EDO Page Mode. EDO Page Mode allows 512 random accesses within a single row with access cycle time as short as 10 ns per 8-bit. These Features make the IS41C8512and IS41LV8512 ideally suited for high-bandwidth graphics, digital signal processing, high-performance puting systems, and peripheral applications. The IS41C8512 is packaged in a 28-pin 400mil SOJ and 400mil TSOP-2.

KEY TIMING PARAMETERS

Parameter

Max. RAS Access Time (t RAC) Max. CAS Access Time (t CAC) Max. Column Address Access Time (t AA) Min. EDO Page Mode Cycle Time (t PC) Min. Read/Write Cycle Time (t RC) -35 35 10 18 12 60 -50 50 14 25 20 90 -60 60 15 30 25 110 Unit ns ns ns ns ns

PIN CON.IGURATIONS 28 Pin SOJ, TSOP-2 PIN DESCRIPTIONS

VCC I/O0 I/O1 I/O2 I/O3 NC WE RAS A9 A0 A1 A2 A3 VCC 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 GND I/O7 I/O6 I/O5 I/O4 CAS OE NC A8 A7 A6 A5 A4 GND

A0-A9 I/O0-7 WE OE RAS CAS Vcc GND NC

Address Inputs Data Inputs/Outputs Write Enable Output Enable Row Address Strobe Column Address Strobe Power Ground No Connection

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution...