ICSSSTV16859 Description

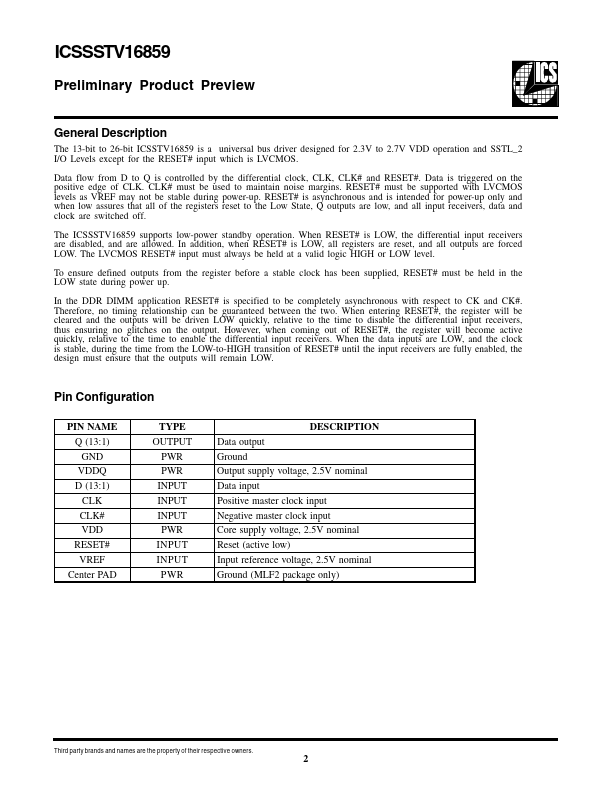

The 13-bit to 26-bit ICSSTV16859 is a universal bus driver designed for 2.3V to 2.7V VDD operation and SSTL_2 I/O Levels except for the RESET# input which is LVCMOS. Data flow from D to Q is controlled by the differential clock, CLK, CLK# and RESET#. Data is triggered on the positive edge of CLK.

ICSSSTV16859 Key Features

- Differential clock signals

- Meets SSTL_2 signal data

- Supports SSTL_2 class II specifications on outputs

- low-voltage operation

- VDD = 2.3V to 2.7V

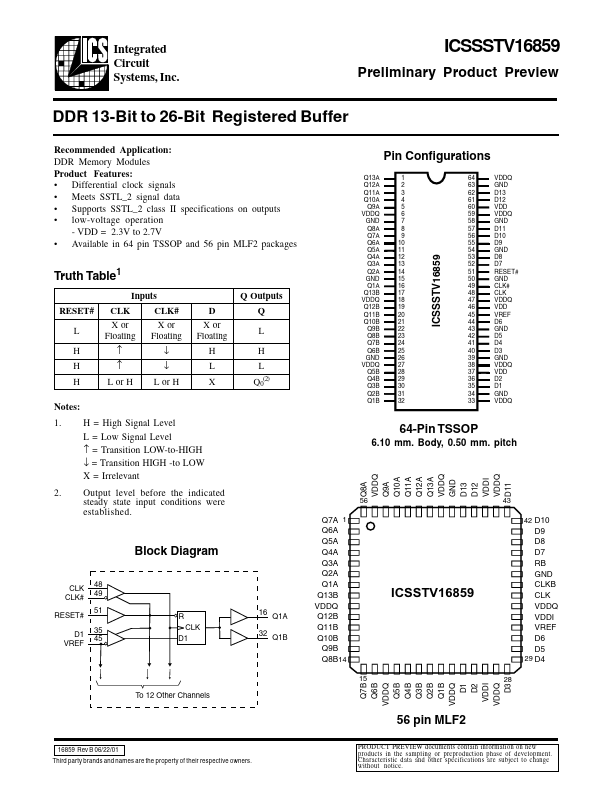

- Available in 64 pin TSSOP and 56 pin MLF2 packages