IDT5V926

IDT5V926 is SINGLE OUTPUT CLOCK GENERATOR manufactured by Integrated Device.

IDT5V926 SINGLE OUTPUT CLOCK GENERATOR

SINGLE OUTPUT CLOCK GENERATOR

INDUSTRIALTEMPERATURERANGE

Features

:

- 3V to 3.6V operating voltage

- 48MHz to 160MHz output frequency range

- Input from fundamental crystal oscillator or external source

- Internal PLL feedback (loading feedback output relative to other outputs, adjusts propagation delay between REF inputs and outputs)

- Select inputs (S[1:0]) for FB divide selection (multiply ratio of 2, 3, 4, 4.25, 5, 6, 6.25, and 8)

- Low jitter

- PLL bypass for testing and power-down control (S1 = H, S0 = H, powers part down <500µA)

- Available in TSSOP package

DESCRIPTION:

The IDT5V926 is a low-cost, low skew, low jitter, and high-performance clock synthesizer with a reference clock from lower frequency crystal or clock input. It has been specially designed to interface with Gigabit Ethernet and Fast Ethernet applications by providing a 125MHz clock from 25MHz input. It can be programmed to provide output frequencies ranging from 48MHz to 160MHz, with input frequencies ranging from 6MHz to 80MHz.

The IDT5V926 includes an internal RC filter that provides excellent jitter characteristics and eliminates the need for external ponents. When using the optional crystal input, the chip accepts a 10

- 40MHz fundamental mode crystal with a maximum equivalent series resistance of 50Ω.

APPLICATIONS:

- Gigabit ethernet

- Router

- Network switches

- SAN

- Instrumentation

- Fibre channel

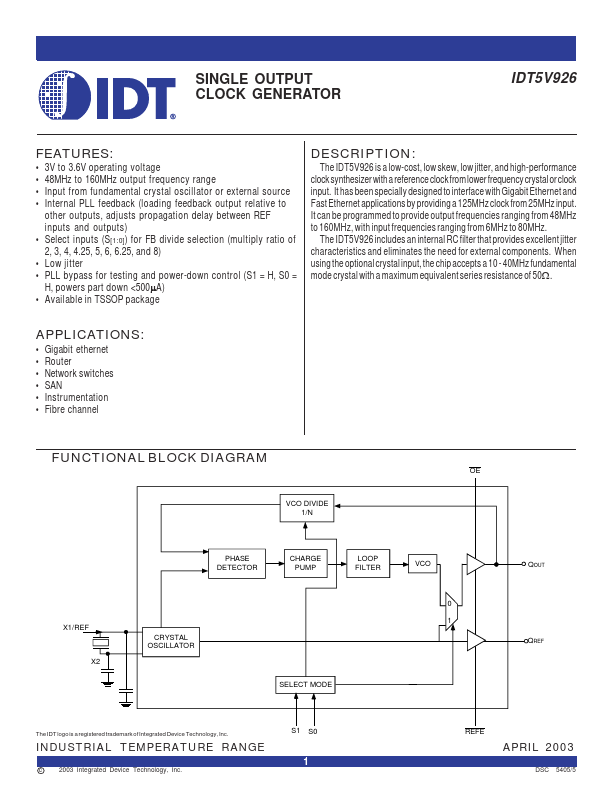

FUNCTIONAL BLOCK DIAGRAM

VCO DIVIDE 1/N

X1/REF X2

PHASE DETECTOR

CHARGE PUMP

CRYSTAL...