IDT79R3500

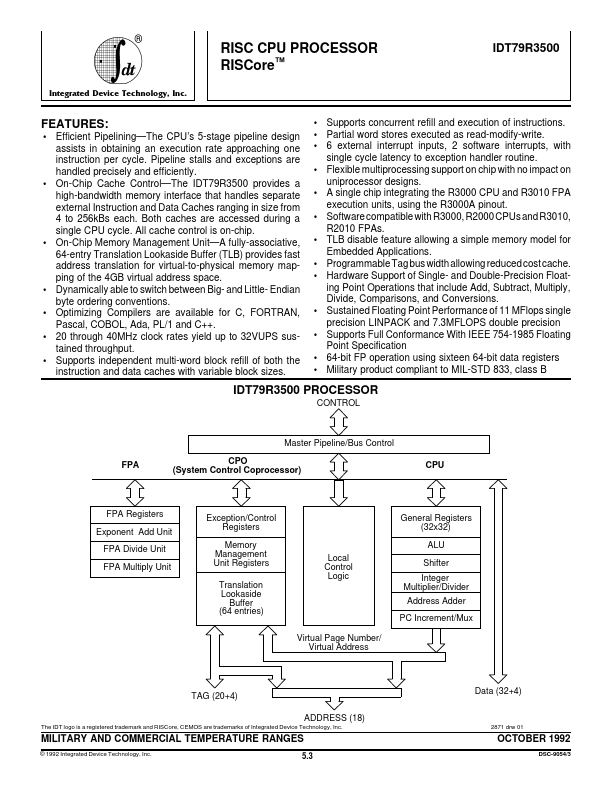

IDT79R3500 is RISC CPU PROCESSOR RISCore manufactured by Integrated Device.

IDT79R3500 RISC CPU PROCESSOR RISCore ®

MILITARY AND MERCIAL TEMPERATURE RANGES

RISC CPU PROCESSOR RISCore™

Integrated Device Technology, Inc.

Features

:

- Efficient Pipelining- The CPU’s 5-stage pipeline design assists in obtaining an execution rate approaching one instruction per cycle. Pipeline stalls and exceptions are handled precisely and efficiently.

- On-Chip Cache Control- The IDT79R3500 provides a high-bandwidth memory interface that handles separate external Instruction and Data Caches ranging in size from 4 to 256kBs each. Both caches are accessed during a single CPU cycle. All cache control is on-chip.

- On-Chip Memory Management Unit- A fully-associative,...