HCTS74MS Key Features

- 3 Micron Radiation Hardened SOS CMOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/ Bit-Day (Typ)

- Dose Rate Survivability: >1 x 1012 RAD (Si)/s

- Dose Rate Upset >10

- Latch-Up Free Under Any Conditions

- Military Temperature Range: -55oC to +125oC

- Significant Power Reduction pared to LSTTL ICs

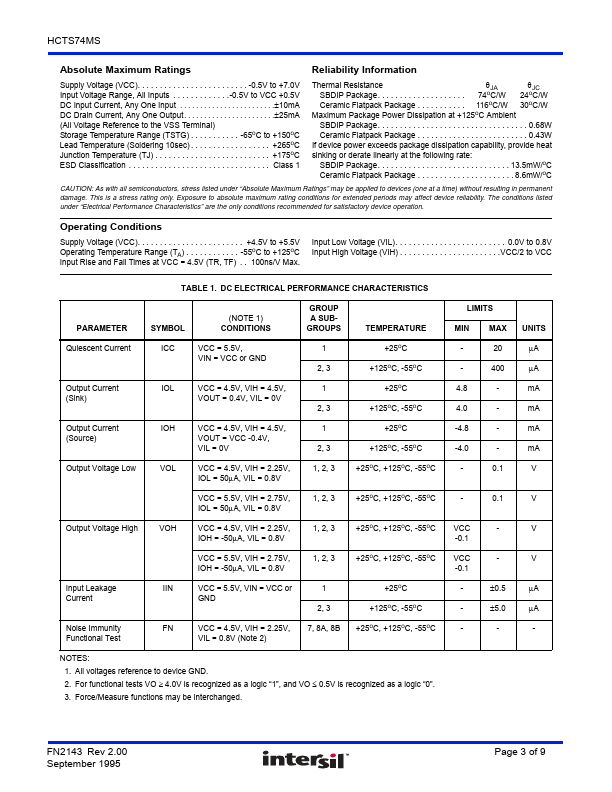

- DC Operating Voltage Range: 4.5V to 5.5V