Datasheet Summary

Data Sheet February 1999 File Number

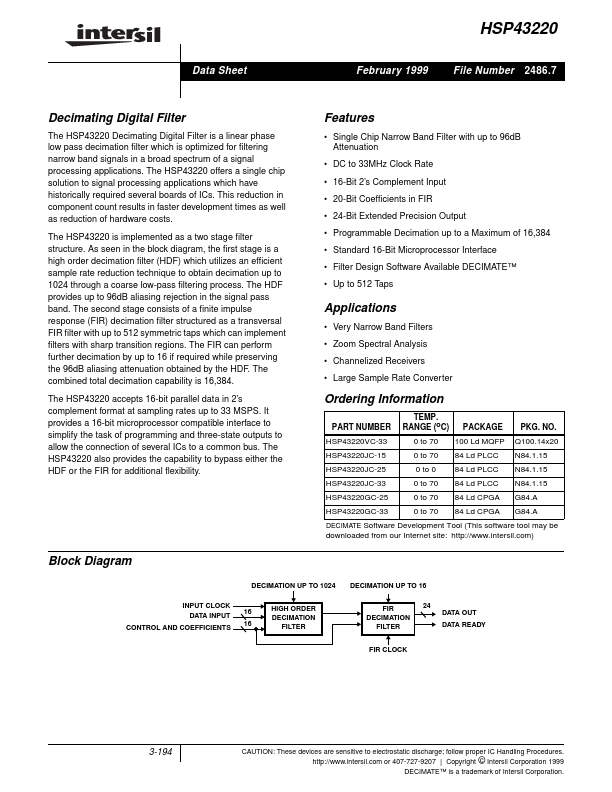

Decimating Digital Filter

The HSP43220 Decimating Digital Filter is a linear phase low pass decimation filter which is optimized for filtering narrow band signals in a broad spectrum of a signal processing applications. The HSP43220 offers a single chip solution to signal processing applications which have historically required several boards of ICs. This reduction in ponent count results in faster development times as well as reduction of hardware costs. The HSP43220 is implemented as a two stage filter structure. As seen in the block diagram, the first stage is a high order decimation filter (HDF) which utilizes an efficient sample rate...