Datasheet Summary

Data Sheet May 1999 File Number

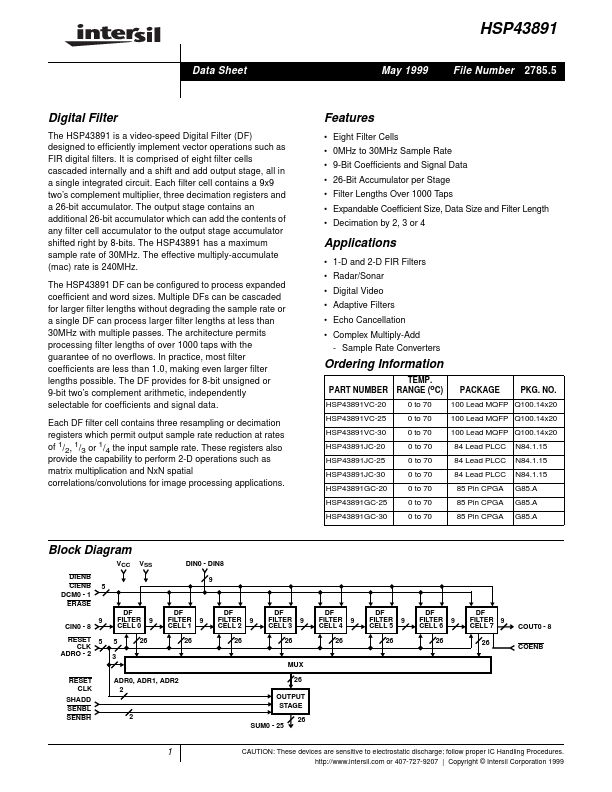

Digital Filter

The HSP43891 is a video-speed Digital Filter (DF) designed to efficiently implement vector operations such as FIR digital filters. It is prised of eight filter cells cascaded internally and a shift and add output stage, all in a single integrated circuit. Each filter cell contains a 9x9 two’s plement multiplier, three decimation registers and a 26-bit accumulator. The output stage contains an additional 26-bit accumulator which can add the contents of any filter cell accumulator to the output stage accumulator shifted right by 8-bits. The HSP43891 has a maximum sample rate of 30MHz. The effective multiply-accumulate...