Datasheet Summary

DEVICES INCORPORATED

12 x 12-bit Parallel Multiplier

DEVICES INCORPORATED

12 x 12-bit Parallel Multiplier

DESCRIPTION

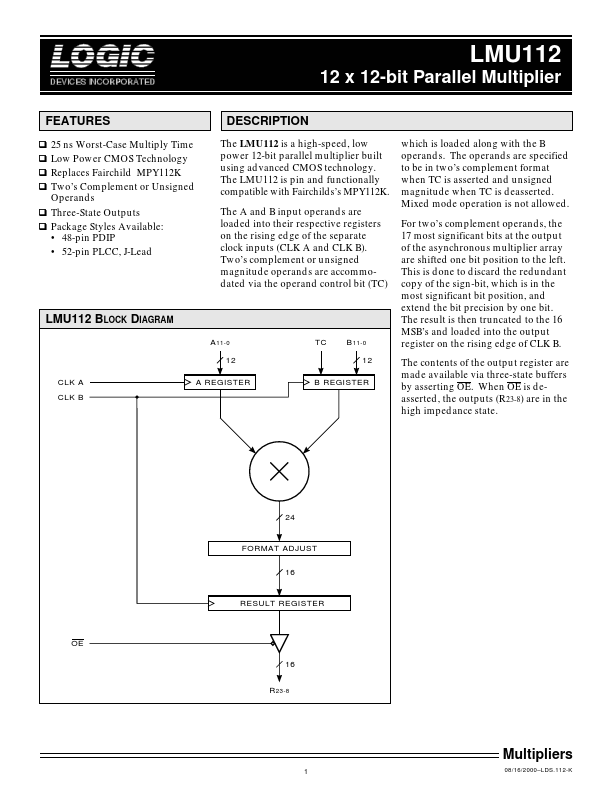

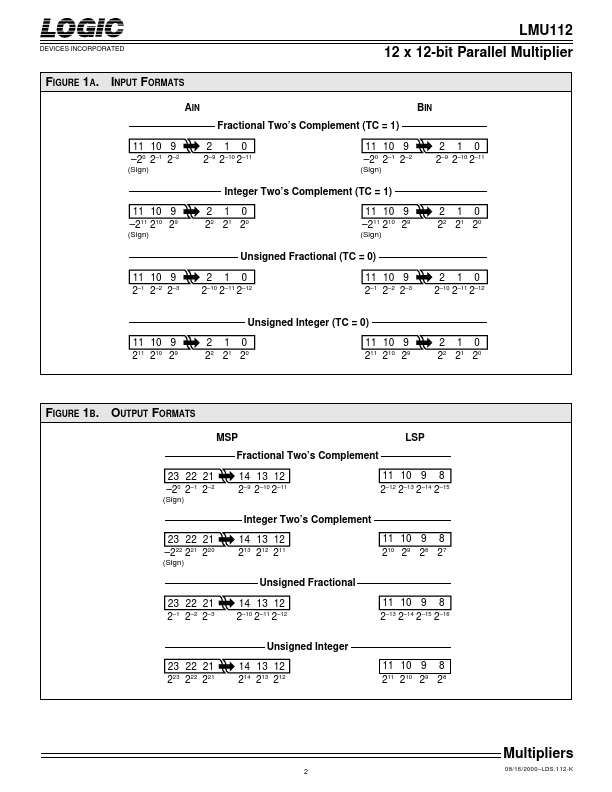

The LMU112 is a high-speed, low power 12-bit parallel multiplier built using advanced CMOS technology. The LMU112 is pin and functionally patible with Fairchilds’s MPY112K. The A and B input operands are loaded into their respective registers on the rising edge of the separate clock inputs (CLK A and CLK B). Two’s plement or unsigned magnitude operands are acmodated via the operand control bit (TC) which is loaded along with the B operands. The operands are specified to be in two’s plement format when TC is asserted and unsigned magnitude when...