Datasheet Summary

DEVICES INCORPORATED

16 x 16-bit Parallel Multiplier

DEVICES INCORPORATED

16 x 16-bit Parallel Multiplier

DESCRIPTION

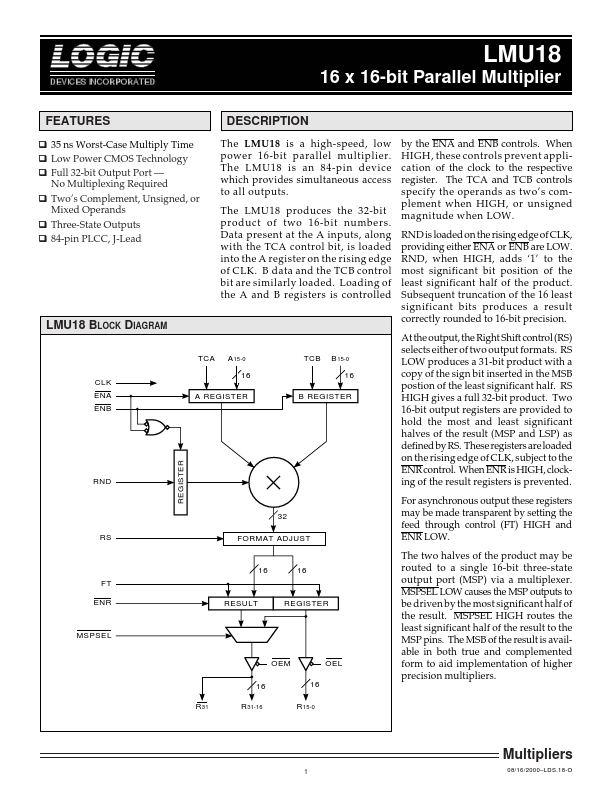

The LMU18 is a high-speed, low power 16-bit parallel multiplier. The LMU18 is an 84-pin device which provides simultaneous access to all outputs. The LMU18 produces the 32-bit product of two 16-bit numbers. Data present at the A inputs, along with the TCA control bit, is loaded into the A register on the rising edge of CLK. B data and the TCB control bit are similarly loaded. Loading of the A and B registers is controlled by the ENA and ENB controls. When HIGH, these controls prevent application of the clock to the respective register. The TCA and TCB...