Datasheet Summary

DEVICES INCORPORATED

16 x 16-bit Parallel Multiplier

DEVICES INCORPORATED

16 x 16-bit Parallel multiplier

DESCRIPTION

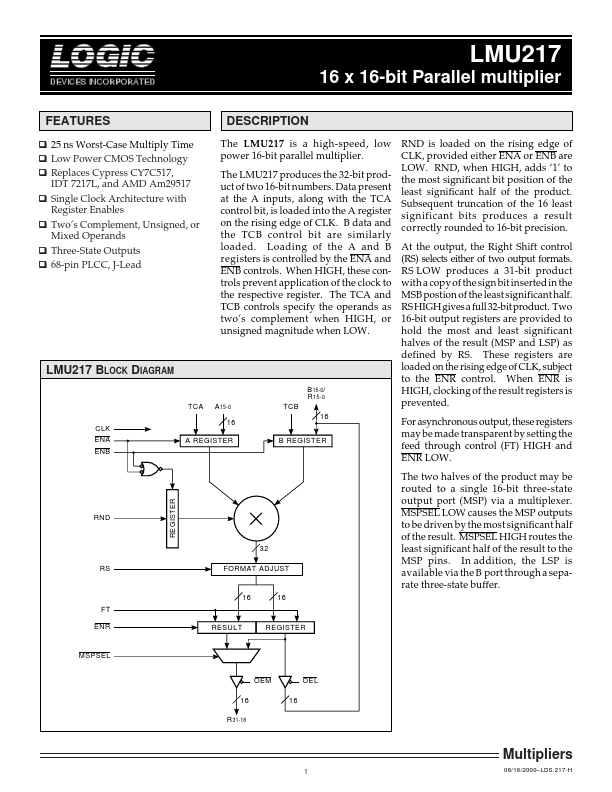

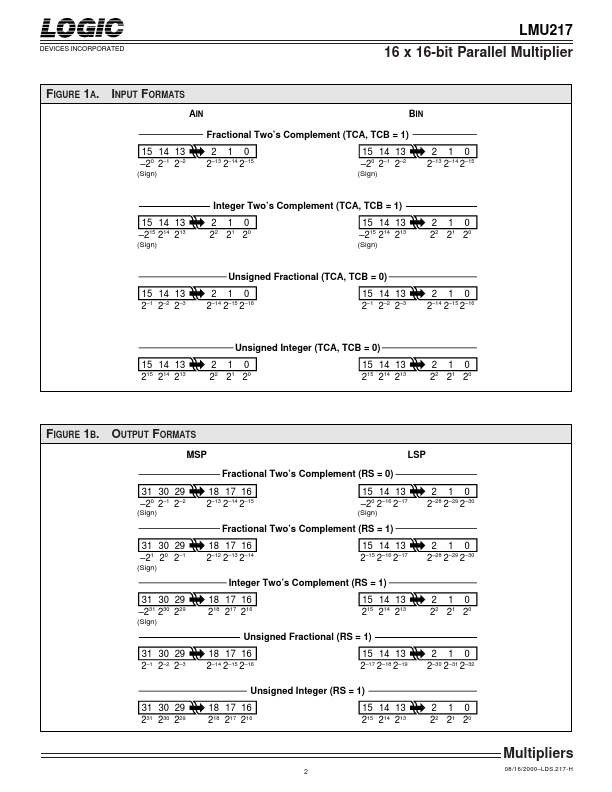

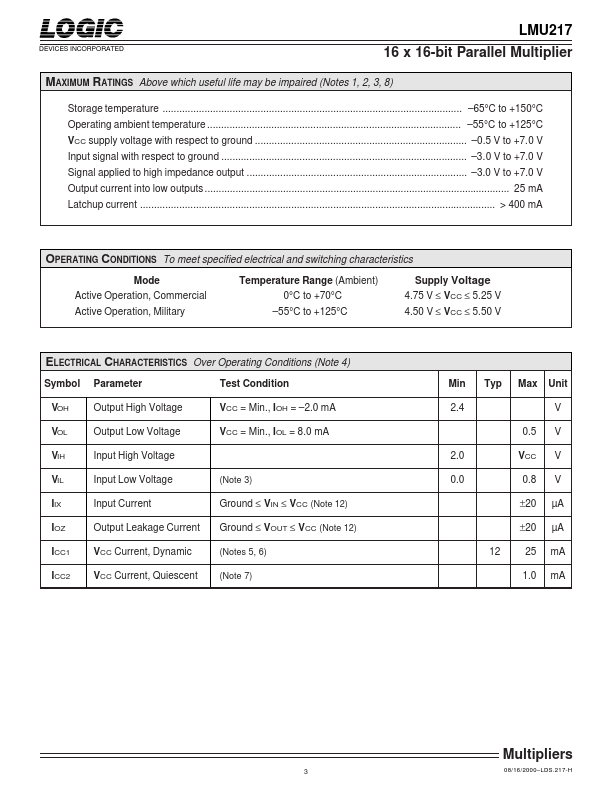

The LMU217 is a high-speed, low RND is loaded on the rising edge of power 16-bit parallel multiplier. CLK, provided either ENA or ENB are LOW. RND, when HIGH, adds ‘1’ to The LMU217 produces the 32-bit prodthe most significant bit position of the uct of two 16-bit numbers. Data present least significant half of the product. at the A inputs, along with the TCA Subsequent truncation of the 16 least control bit, is loaded into the A register significant bits produces a result on the rising edge of CLK. B data and correctly rounded to 16-bit precision. the TCB...