SY100E154

SY100E154 is 5-BIT 2:1 MUX-LATCH manufactured by Micrel Semiconductor.

Micrel, Inc.

5-BIT 2:1 MUX-LATCH

SY10E154

SY1S0YE10105E4154 SY100E154

Features s 750ps max. LEN to output s Extended 100E VEE range of

- 4.2V to

- 5.5V s 700ps max. D to output s Differential outputs s Asynchronous Master Reset s Dual latch-enables s Fully patible with industry standard 10KH,

100K ECL levels s Internal 75KΩ input pulldown resistors s Fully patible with Motorola MC10E/100E154 s Available in 28-pin PLCC package

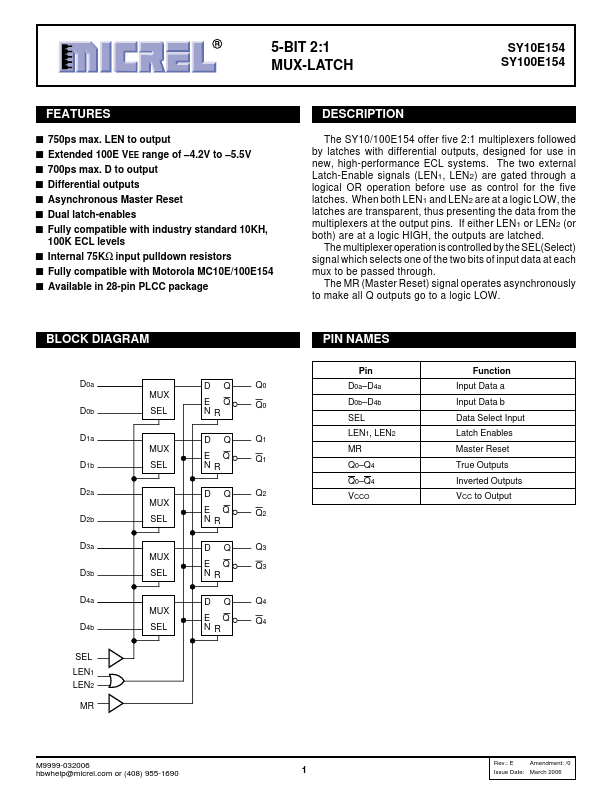

BLOCK DIAGRAM

D0a D0b D1a D1b D2a D2b D3a D3b D4a D4b

SEL LEN1 LEN2

MUX SEL

MUX SEL

MUX SEL

MUX SEL

MUX SEL

DQ EQ NR

DQ EQ NR

DQ EQ NR

DQ EQ NR

DQ EQ NR

Q0 Q0

Q1 Q1

Q2 Q2

Q3 Q3

Q4 Q4

DESCRIPTION

The SY10/100E154 offer five 2:1 multiplexers followed by latches with differential outputs, designed for use in new, high-performance ECL systems. The two external Latch-Enable signals (LEN1, LEN2) are gated through a logical OR operation before use as control for the five latches. When both LEN1 and LEN2 are at a logic LOW, the latches are transparent, thus presenting the data from the multiplexers at the output pins. If either LEN1 or LEN2 (or both) are at a logic HIGH, the outputs are latched.

The multiplexer operation is controlled by the SEL(Select) signal which selects one of the two bits of input data at each mux to be passed through.

The MR (Master Reset) signal operates asynchronously to make all Q outputs go to a logic...