ML6510

ML6510 is Series Programmable Adaptive Clock Manager (PACMan) manufactured by Micro Linear.

DESCRIPTION

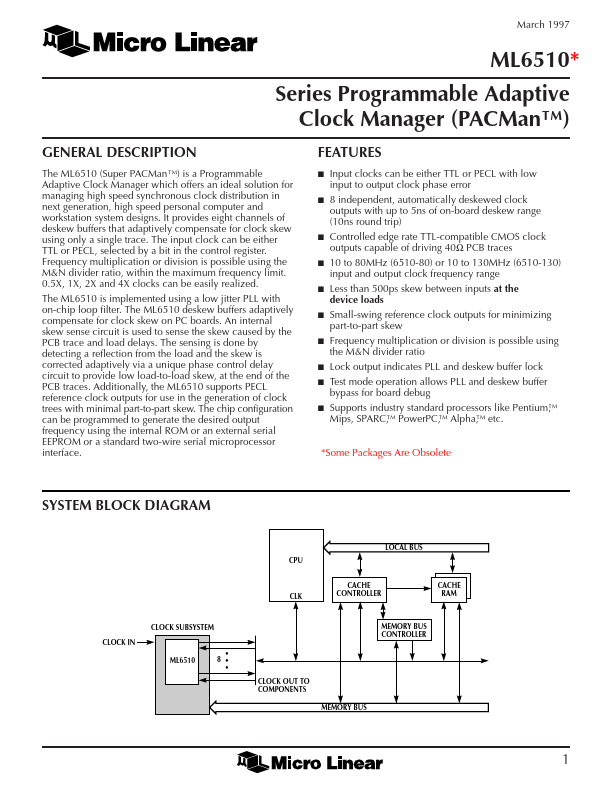

The ML6510 (Super PACMan™) is a Programmable Adaptive Clock Manager which offers an ideal solution for managing high speed synchronous clock distribution in next generation, high speed personal puter and workstation system designs. It provides eight channels of deskew buffers that adaptively pensate for clock skew using only a single trace. The input clock can be either TTL or PECL, selected by a bit in the control register. Frequency multiplication or division is possible using the M&N divider ratio, within the maximum frequency limit. 0.5X, 1X, 2X and 4X clocks can be easily realized. The ML6510 is implemented using a low jitter PLL with on-chip loop filter. The ML6510 deskew buffers adaptively pensate for clock skew on PC boards. An internal skew sense circuit is used to sense the skew caused by the PCB trace and load delays. The sensing is done by detecting a reflection from the load and the skew is corrected adaptively via a unique phase control delay circuit to provide low load-to-load skew, at the end of the PCB traces. Additionally, the ML6510 supports PECL reference clock outputs for use in the generation of clock trees with minimal part-to-part skew. The chip configuration can be programmed to generate the desired output frequency using the internal ROM or an external serial EEPROM or a standard two-wire serial microprocessor interface.

FEATURES s s

Input clocks can be either TTL or PECL with low input to output clock phase error 8 independent, automatically deskewed clock outputs with up to 5ns of on-board deskew range (10ns round trip) Controlled edge rate TTL-patible CMOS clock outputs capable of driving 40Ω PCB traces 10 to 80MHz (6510-80) or 10 to 130MHz (6510-130) input and output clock frequency range Less than 500ps skew between inputs at the device loads Small-swing reference clock outputs for minimizing part-to-part skew Frequency multiplication or division is possible using the M&N divider ratio Lock output indicates PLL and...