ML6516244

ML6516244 is 16-Bit Buffer/Line Driver with 3-State Outputs manufactured by Micro Linear.

DESCRIPTION

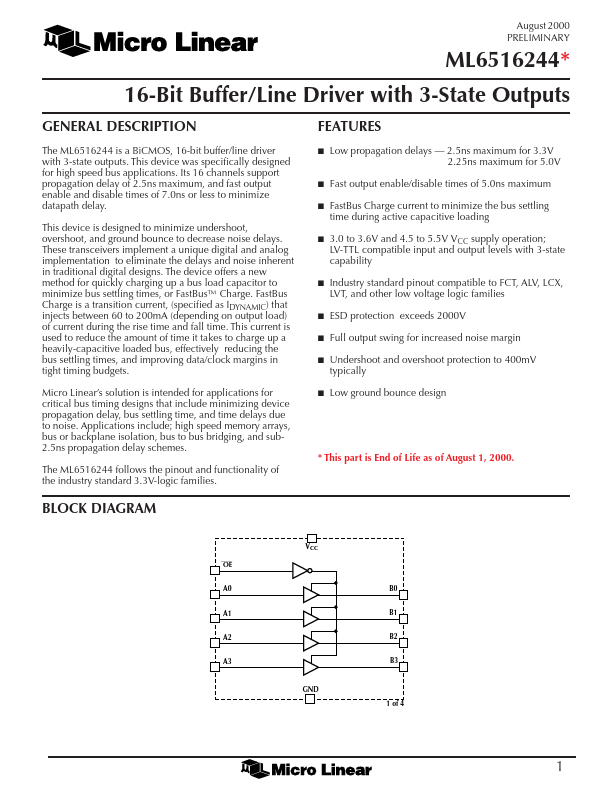

The ML6516244 is a Bi CMOS, 16-bit buffer/line driver with 3-state outputs. This device was specifically designed for high speed bus applications. Its 16 channels support propagation delay of 2.5ns maximum, and fast output enable and disable times of 7.0ns or less to minimize datapath delay. This device is designed to minimize undershoot, overshoot, and ground bounce to decrease noise delays. These transceivers implement a unique digital and analog implementation to eliminate the delays and noise inherent in traditional digital designs. The device offers a new method for quickly charging up a bus load capacitor to minimize bus settling times, or Fast Bus™ Charge. Fast Bus Charge is a transition current, (specified as IDYNAMIC) that injects between 60 to 200m A (depending on output load) of current during the rise time and fall time. This current is used to reduce the amount of time it takes to charge up a heavily-capacitive loaded bus, effectively reducing the bus settling times, and improving data/clock margins in tight timing budgets. Micro Linear’s solution is intended for applications for critical bus timing designs that include minimizing device propagation delay, bus settling time, and time delays due to noise. Applications include; high speed memory arrays, bus or backplane isolation, bus to bus bridging, and sub2.5ns propagation delay schemes. The ML6516244 follows the pinout and functionality of the industry standard 3.3V-logic families.

FEATURES s

Low propagation delays

- 2.5ns maximum for 3.3V 2.25ns maximum for 5.0V Fast output enable/disable times of 5.0ns maximum Fast Bus Charge current to minimize the bus settling time during active capacitive loading 3.0 to 3.6V and 4.5 to 5.5V VCC supply operation; LV-TTL patible input and output levels with 3-state capability Industry standard pinout patible to FCT, ALV, LCX, LVT, and other low voltage logic families ESD protection exceeds 2000V Full output swing for increased noise margin Undershoot and...