MT46V32M4

MT46V32M4 is (MT46Vxxx) DOUBLE DATA RATE DDR SDRAM manufactured by Micron Technology.

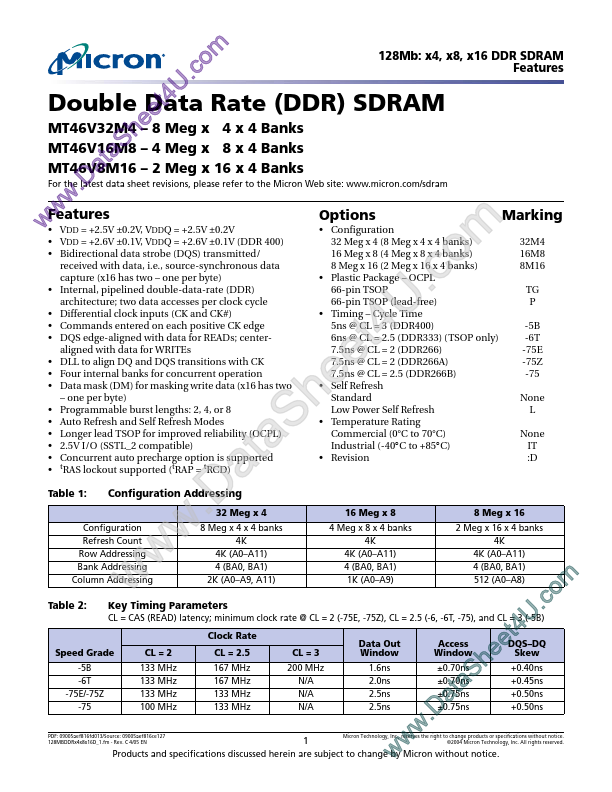

m 128Mb: x4, x8, x16 DDR SDRAM o Features c . U 4 t Double Data Rate (DDR) SDRAM e e8 Meg x 4 x 4 Banks MT46V32M4h

- S

- 4 Meg x 8 x 4 Banks MT46V16M8 a MT46V8M16 at

- 2 Meg x 16 x 4 Banks .D w w Features

Options Marking w

For the latest data sheet revisions, please refer to the Micron Web site: .micron./sdram

- VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V

- VDD = +2.6V ±0.1V, VDDQ = +2.6V ±0.1V (DDR 400)

- Bidirectional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture (x16 has two

- one per byte)

- Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- mands entered on...