- Part: MT54W2MH18B

- Description: SRAM 2-WORD BURST

- Manufacturer: Micron Technology

- Size: 567.42 KB

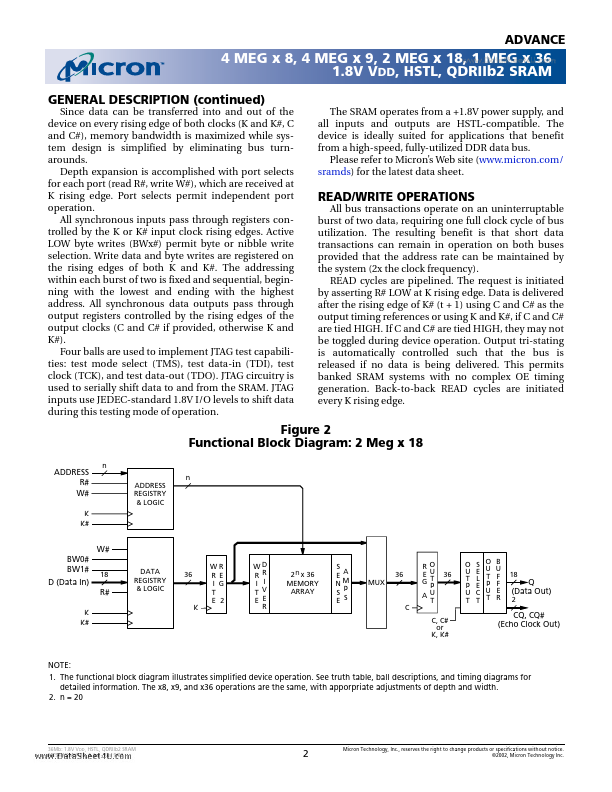

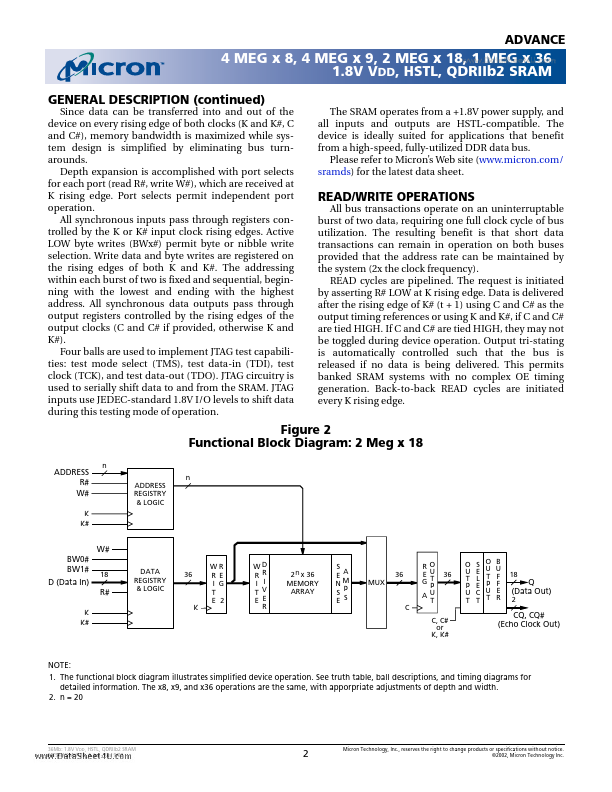

Page 2

Page 2

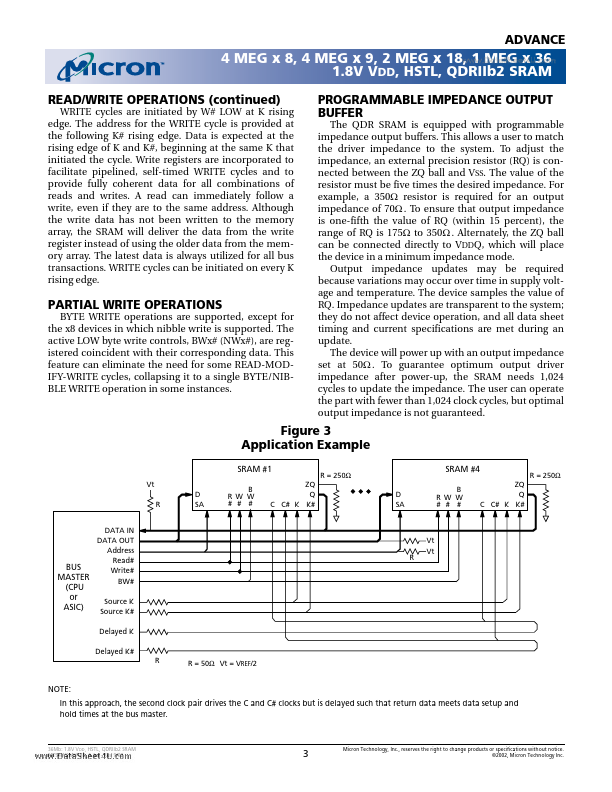

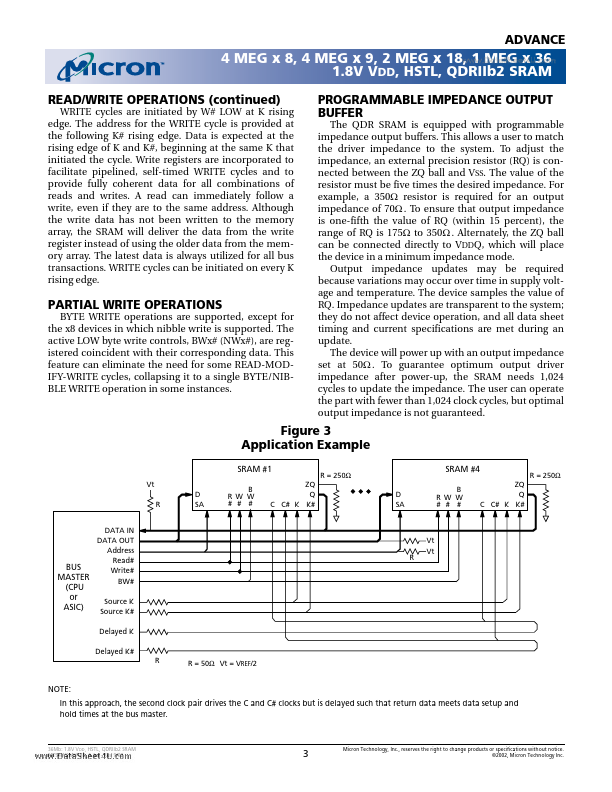

Page 3

Page 3

MT54W2MH18B Key Features

- DLL circuitry for accurate output data placement

- Separate independent read and write data ports with concurrent transactions

- 100 percent bus utilization DDR READ and WRITE operation

- Fast clock to valid data times

- Full data coherency, providing most current data

- Two-tick burst counter for low DDR transaction size

- Double data rate operation on read and write ports

- Two input clocks (K and K#) for precise DDR timing at clock rising edges only

- Two output clocks (C and C#) for precise flight time and clock skew matching-clock and data delivered together to receiv

- Single address bus

Related Micron Technology Datasheets