MT5C2564 Overview

Description

The MT5C2564 is organized as a 65,536 x 4 SRAM using a four-transistor memory cell with a high-speed, low-power CMOS proc.

Key Features

- High-performance, low-power, CMOS double-metal process

- Single +5V ±10% power supply

- Easy memory expansion with CE option

- All inputs and outputs are TTL-compatible OPTIONS

- Timing IOns access 12ns access 15ns access 20ns access 25ns access 35ns access

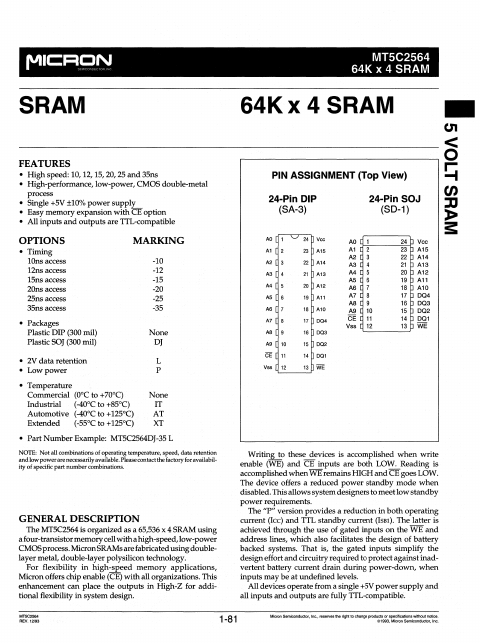

- Packages Plastic DIP (300 mil) Plastic SOJ (300 mil) MARKING

- 2V data retention

- Lowpower L P

- Temperature Commercial (O°C to +70°C) Industrial (-40°C to +85°C) Automotive (-40°C to +125°C) Extended (-55°C to +125°C) None IT AT XT