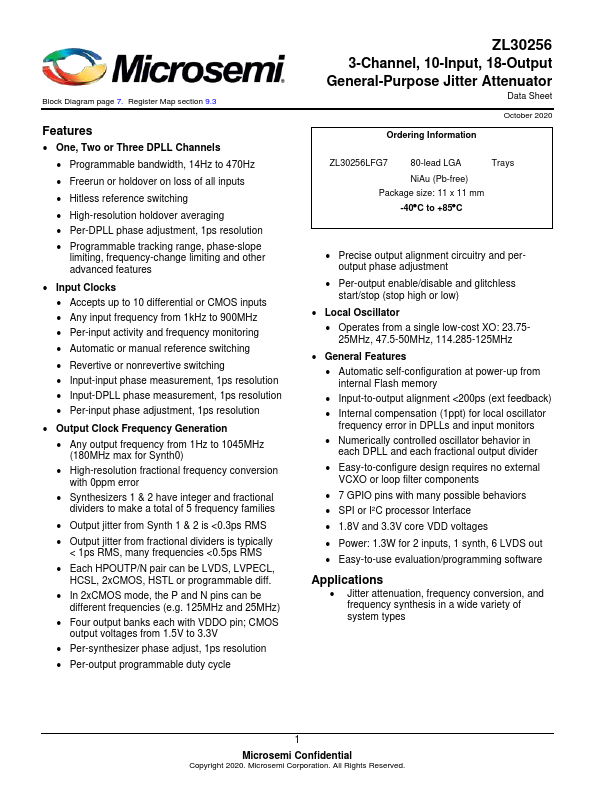

ZL30256

Features

- One, Two or Three DPLL Channels

- Programmable bandwidth, 14Hz to 470Hz

- Freerun or holdover on loss of all inputs

- Hitless reference switching

- High-resolution holdover averaging

- Per-DPLL phase adjustment, 1ps resolution

- Programmable tracking range, phase-slope limiting, frequency-change limiting and other advanced features

- Input Clocks

- Accepts up to 10 differential or CMOS inputs

- Any input frequency from 1k Hz to 900MHz

- Per-input activity and frequency monitoring

- Automatic or manual reference switching

- Revertive or nonrevertive switching

- Input-input phase measurement, 1ps resolution

- Input-DPLL phase measurement, 1ps resolution

- Per-input phase adjustment, 1ps resolution

- Output Clock Frequency Generation

- Any output frequency from 1Hz to 1045MHz (180MHz max for Synth0)

- High-resolution fractional frequency conversion with 0ppm error

- Synthesizers 1 & 2 have integer and fractional dividers to make a total of 5 frequency families

- Output jitter...