M5M4V16169DTP-15

M5M4V16169DTP-15 is 16M (1M-WORD BY 16-BIT) CACHED DRAM manufactured by Mitsubishi Electric.

- Part of the M5M4V16169DTP comparator family.

- Part of the M5M4V16169DTP comparator family.

MITSUBISHI LSIs

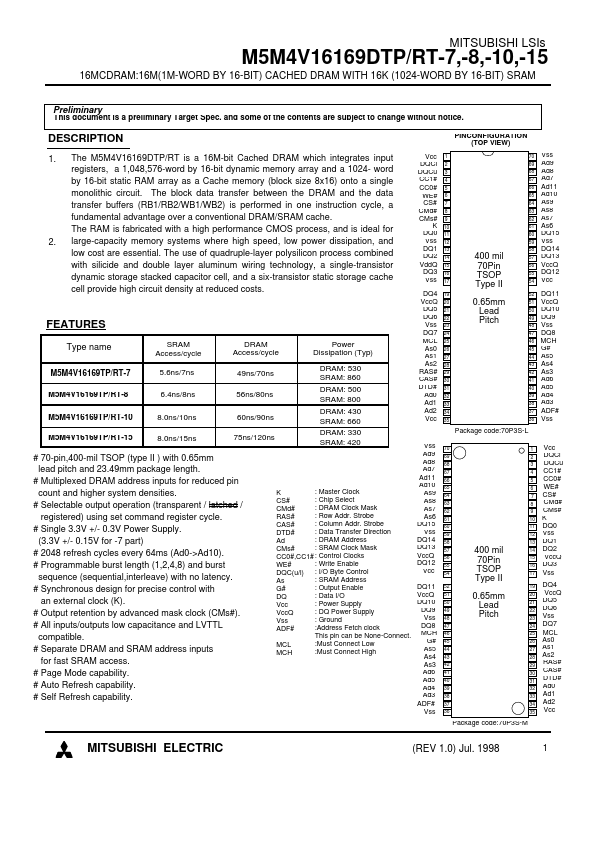

M5M4V16169DTP/RT-7,-8,-10,-15

16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

Preliminary This document is a preliminary Target Spec. and some of the contents are subject to change without notice.

DESCRIPTION

PINCONFIGURATION (TOP VIEW)

1. The M5M4V16169DTP/RT is a 16M-bit Cached DRAM which integrates input registers, a 1,048,576-word by 16-bit dynamic memory array and a 1024- word by 16-bit static RAM array as a Cache memory (block size 8x16) onto a single monolithic circuit. The block data transfer between the DRAM and the data transfer buffers (RB1/RB2/WB1/WB2) is performed in one instruction cycle, a fundamental advantage over a...