Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MCM69D618/D

64K x 18 Bit Synchronous Dual I/O, Dual Address SRAM

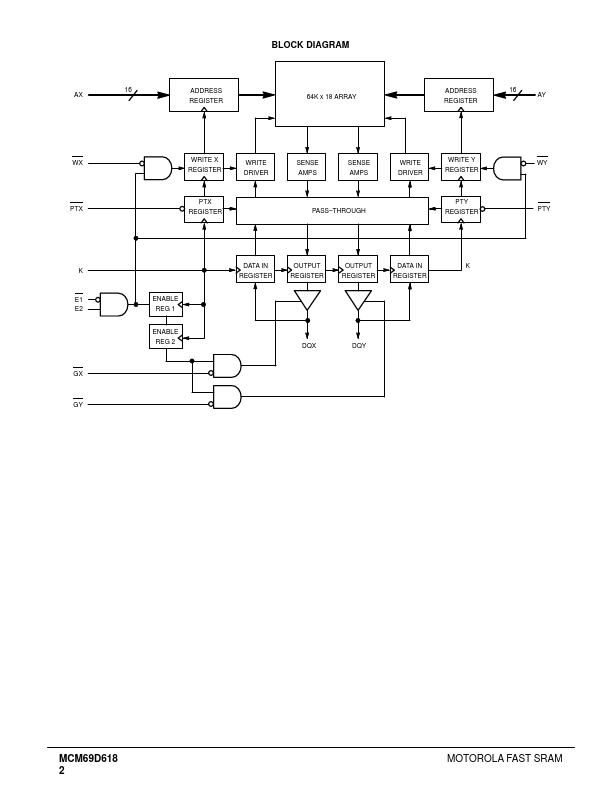

The MCM69D618 is a 1M- bit static random access memory, organized as 64K words of 18 bits. It Features mon data input and data output buffers and incorporates input and output registers on- board with high speed SRAM. The MCM69D618 allows the user to concurrently perform reads, writes, or pass- through cycles in bination on the two data ports. The two address ports (AX, AY) determine the read or write locations for their respective data ports (DQX, DQY). The synchronous design allows for precise cycle control with the use of an external single clock (K). All...