MMDF2N06V Overview

Key Features

- On–resistance Area Product about One–half that of Standard MOSFETs with New Low Voltage, Low RDS(on) Technology

- Avalanche Energy Specified

- IDSS and VDS(on) Specified at Elevated Temperature

- Static Parameters are the Same for both TMOS V and TMOS E–FET

- Miniature SO–8 Surface Mount Package – Saves Board Space

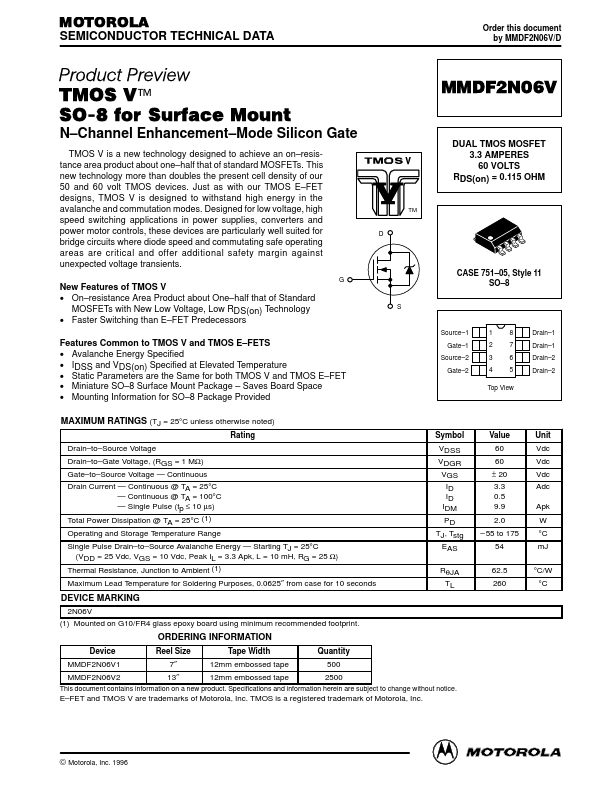

- Mounting Information for SO–8 Package Provided Rating Drain–to–Source Voltage Drain–to–Gate Voltage, (RGS = 1 MΩ) Gate–to–Source Voltage

- Continuous Drain Current

- Continuous @ TA = 25°C Drain Current

- Continuous @ TA = 100°C Drain Current

- Starting TJ = 25°C (VDD = 25 Vdc, VG