MPC962308

MPC962308 is 3.3 V Zero Delay Buffer manufactured by Motorola Semiconductor.

Features

- -

- -

- -

- -

- -

- -

- -

- 1:8 outputs LVCMOS zero-delay buffer Zero input-output propagation delay, adjustable by the capacitive load on FBK input Multiple Configurations, see Table 2. Available MPC962308 Configurations Multiple low-skew outputs 200 ps max output-output skew 700 ps max device-device skew Two banks of four outputs, output tristate control by two select inputs Supports a clock I/O frequency range of 10 MHz to 133 MHz Low jitter, 200 ps max cycle-cycle (-1, -1H, -4, -5H) ±250 ps static phase offset (SPO) 16-pin SOIC package or 16-pin TSSOP package Single 3.3 V supply Ambient temperature range:

- 40°C to +85°C patible with the CY2308 and CY23S08 Spread spectrum patible

..

Freescale Semiconductor, Inc...

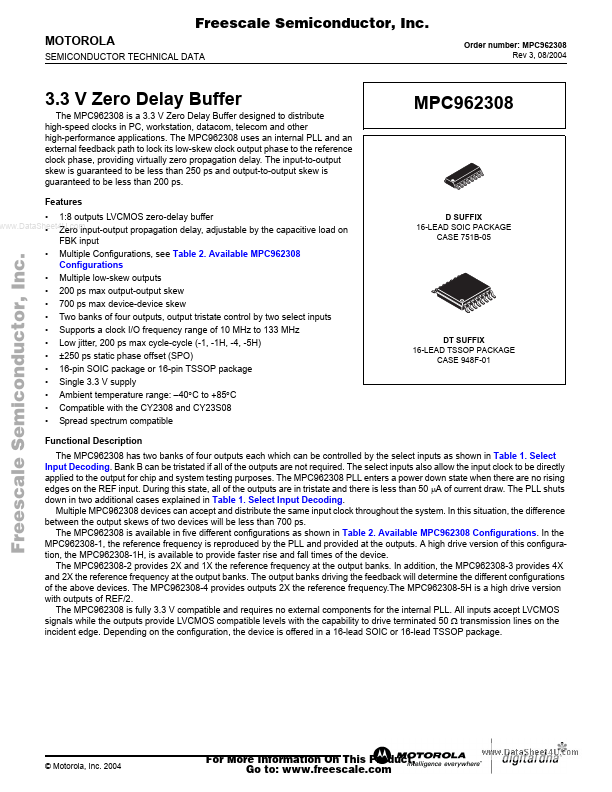

D SUFFIX 16-LEAD SOIC PACKAGE CASE 751B-05

DT SUFFIX 16-LEAD TSSOP PACKAGE CASE 948F-01

Functional Description

The MPC962308 has two banks of four outputs each which can be controlled by the select inputs as shown in Table 1. Select Input Decoding. Bank B can be tristated if all of the outputs are not required. The select inputs also allow the input clock to be directly applied to the output for chip and system testing purposes. The MPC962308 PLL enters a power down state when there are no rising edges on the REF input. During this state, all of the outputs are in tristate and there is less than 50 µA of current draw. The PLL shuts down in two additional cases explained in Table 1. Select Input Decoding. Multiple MPC962308 devices can accept and distribute the same input clock throughout the system. In this situation, the difference between the output skews of two devices will be less than 700 ps. The MPC962308 is available in five different configurations as shown in Table 2. Available MPC962308 Configurations. In the MPC962308-1, the reference frequency is reproduced by the PLL and provided at the outputs. A high drive version of this configuration, the MPC962308-1H, is available to provide faster rise and fall times of the...