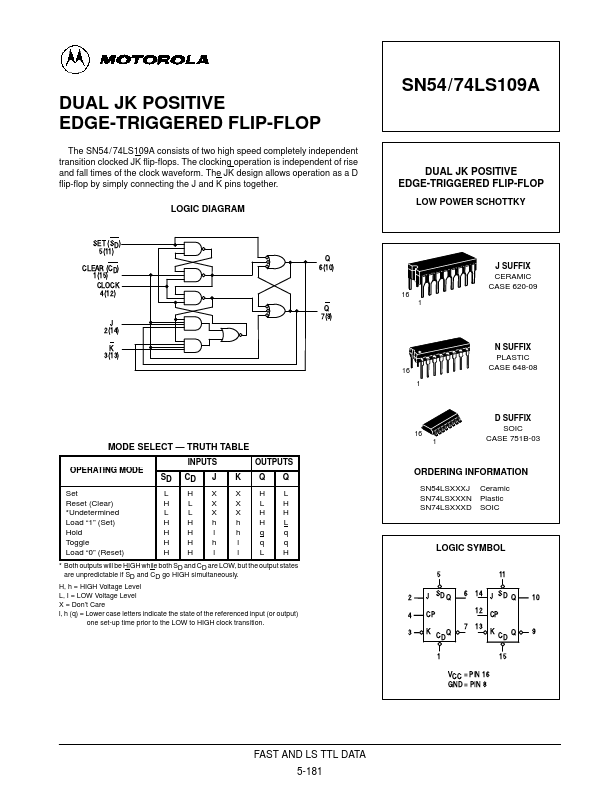

| Part | SN74LS109A |

|---|---|

| Description | DUAL JK POSITIVE EDGE-TRIGGERED FLIP-FLOP |

| Manufacturer | Motorola Semiconductor |

| Size | 147.54 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SN74LS109A | onsemi | Dual JK Positive Edge-Triggered Flip-Flop |

| SN74LS109A | Texas Instruments | Dual J-K Positive-Edge-Triggered Flip-Flops |

| SN74LS109 | onsemi | LOW POWER SCHOTTKY |

| SN74LS10 | onsemi | TRIPLE 3-INPUT NAND GATE |

| SN74LS107A | Texas Instruments | DUAL J-K FLIP-FLOPS |