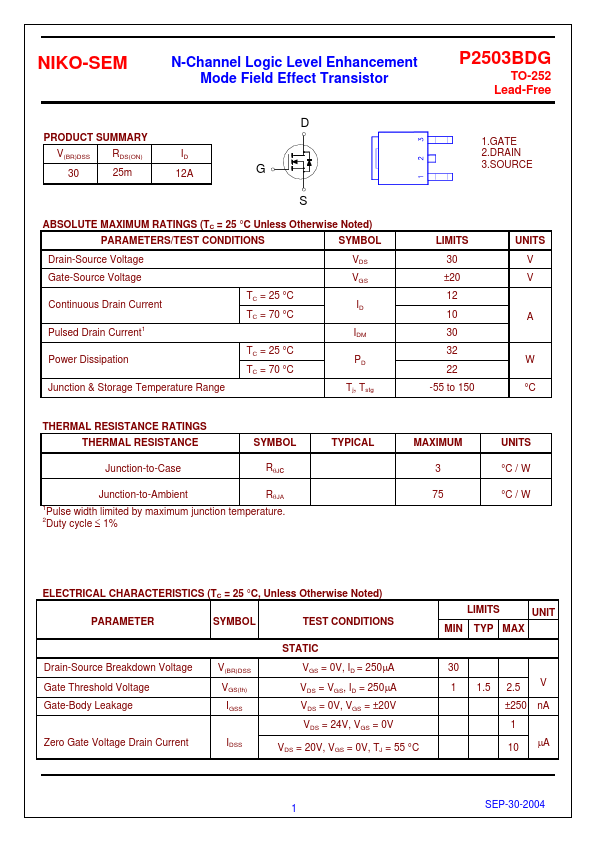

| Part | P2503BDG |

|---|---|

| Description | N-Channel Logic FET |

| Manufacturer | NIKO-SEM |

| Size | 283.31 KB |

Pricing from 0.1523 USD, available from UnikeyIC and Unikeyic (ICkey).

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| UnikeyIC | 400000 | 100+ : 0.1523 USD 200+ : 0.1498 USD 300+ : 0.1459 USD |

View Offer |

| Unikeyic (ICkey) | 400000 | 100+ : 0.1523 USD 200+ : 0.1498 USD 300+ : 0.1459 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| P2503BDG | UNIKC | N-Channel MOSFET |

| P2503NVG | UNIKC | N&P-Channel MOSFET |

| P2503HVG | UNIKC | N-Channel MOSFET |

| P2503HEA | UNIKC | MOSFET |

| P2500M | Taiwan Semiconductor | Glass Passivated Rectifier |