PHD38N02LT

PHD38N02LT is TrenchMOS logic level FET manufactured by NXP Semiconductors.

Description

N-channel logic level field-effect transistor in a plastic package using Trench MOS™ technology. Product availability: PHB38N02LT in SOT404 (D2-PAK) PHD38N02LT in SOT428 (D-PAK).

1.2 Features s Low on-state resistance s 2.5 V gate drive.

1.3 Applications s Linear regulator for DDR memory.

1.4 Quick reference data s VDS = 20 V s Ptot = 57.6 W s ID = 44.7 A s RDSon ≤ 16 mΩ

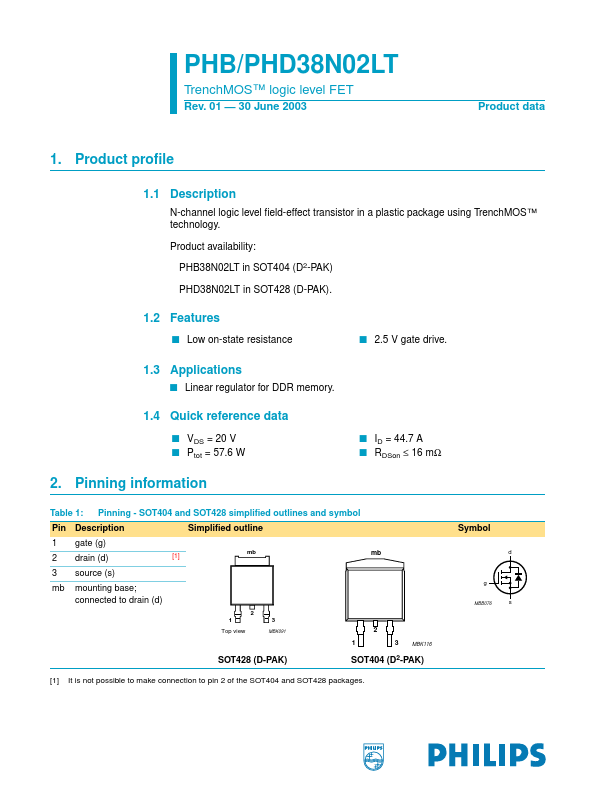

2. Pinning information

Table 1: 1 2 3 mb Pinning

- SOT404 and SOT428 simplified outlines and symbol Simplified outline

[1] mb

Pin Description gate (g) drain (d) source (s) mounting base; connected to drain (d)

Symbol mb d g s

MBB076

2 1 Top view 3

MBK091

2 1 3

MBK116

SOT428 (D-PAK)

[1]

SOT404 (D2-PAK)

It is not possible to make connection to pin 2 of the SOT404 and SOT428 packages.

Philips Semiconductors

PHB/PHD38N02LT

Trench MOS™ logic level FET

3. Limiting values

Table 2: Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Symbol Parameter VDS VDGR VGS ID IDM Ptot Tstg Tj IS ISM drain-source voltage (DC) drain-gate voltage (DC) gate-source voltage (DC) drain current (DC) peak drain current total power dissipation storage temperature junction temperature source (diode forward) current (DC) Tmb = 25 °C peak source (diode forward) current Tmb = 25 °C; pulsed; tp ≤ 10 µs Tmb = 25 °C; VGS = 5 V; Figure 2 and 3 Tmb = 100 °C; VGS = 5 V; Figure 2 Tmb = 25 °C; pulsed; tp ≤ 10 µs; Figure 3 Tmb = 25 °C; Figure 1 Conditions 25 °C ≤ Tj ≤ 175 25 °C ≤ Tj ≤ 175 o C o C;

Min RGS = 20 kΩ

- 55

- 55

- Max 20 20 12 44.7 31.6 179 57.6 +175 +175 44.7 179

Unit V V V A A A W °C °C A A

Source-drain diode

9397 750 11614

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 01

- 30 June 2003

2 of 13

Philips Semiconductors

PHB/PHD38N02LT

Trench MOS™ logic level...