DM54LS503 Overview

Description

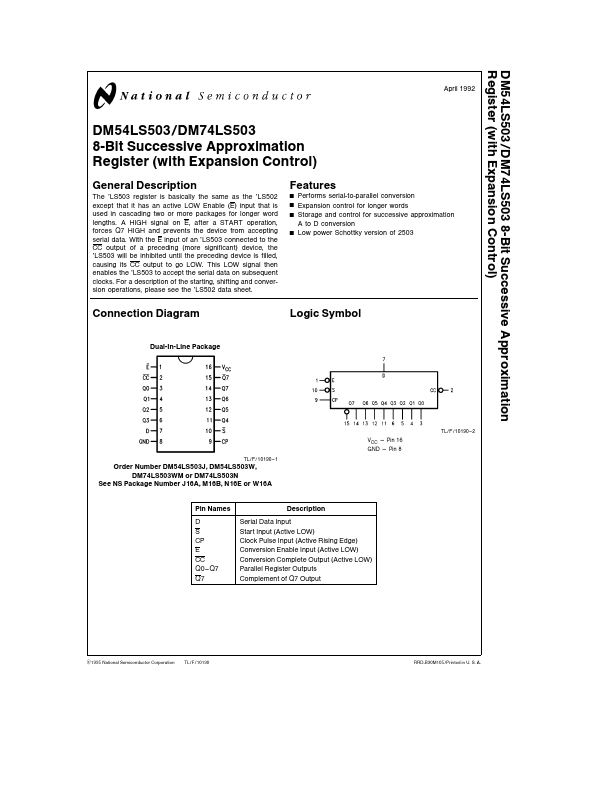

The ’LS503 register is basically the same as the ’LS502 except that it has an active LOW Enable (E) input that is used in cascading two or more packages for longer word lengths A HIGH signal on E after a START operation forces Q7 HIGH and prevents the device from accepting serial data With the E input of an ’LS503 connected to the CC output of a preceding (more significant) device the ’LS503 will be inhibited until the preceding device is filled causing its CC output to go LOW This LOW signal then enables the ’LS503 to accept the serial data on subsequent clocks For a description of the starting shifting and conversion operations please see the ’LS502 data sheet.

Key Features

- Y Performs serial-to-parallel conversion Y Expansion control for longer words Y Storage and control for