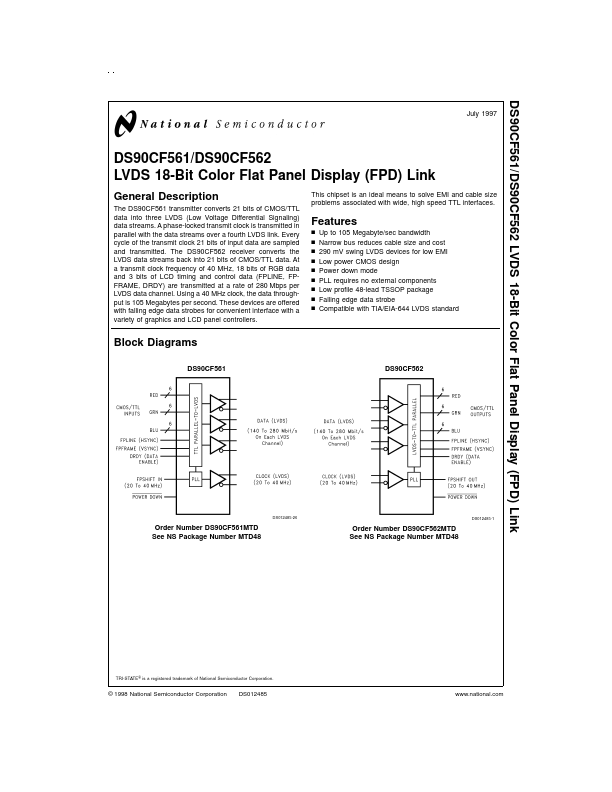

- Part: DS90CF561

- Description: LVDS 18-Bit Color Flat Panel Display Link

- Manufacturer: National Semiconductor

- Size: 244.85 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| DS90CF564 | Texas Instruments | LVDS |

| DS90CF563 | Texas Instruments | LVDS |