DS90CR286A

Overview

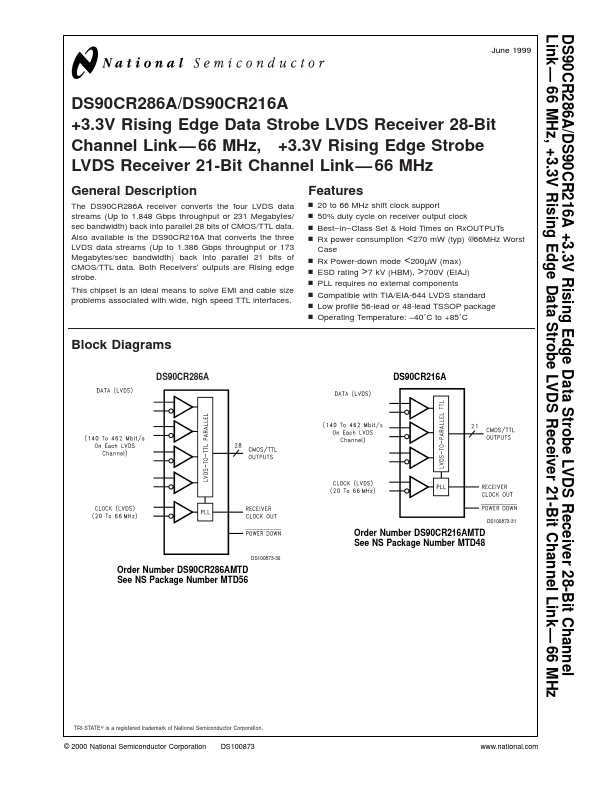

The DS90CR286A receiver converts the four LVDS data streams (Up to 1.848 Gbps throughput or 231 Megabytes/ sec bandwidth) back into parallel 28 bits of CMOS/TTL data. Also available is the DS90CR216A that converts the three LVDS data streams (Up to 1.386 Gbps throughput or 173 Megabytes/sec bandwidth) back into parallel 21 bits of CMOS/TTL data.

- n n n n n n n n

- 20 to 66 MHz shift clock support 50% duty cycle on receiver output clock Best-in-Class Set & Hold Times on RxOUTPUTs Rx power consumption < 270 mW (typ) @66MHz Worst Case Rx Power-down mode < 200µW (max) ESD rating > 7 kV (HBM), > 700V (EIAJ) PLL requires no external components Compatible with TIA/EIA-644 LVDS standard Low profile 56-lead or 48-lead TSSOP package Operating Temperature: -40˚C to +85˚C Block Diagrams