74F109

74F109 is Dual JK Positive Edge-Triggered Flip-Flop manufactured by National Semiconductor.

- Part of the 74F109PC comparator family.

- Part of the 74F109PC comparator family.

Description

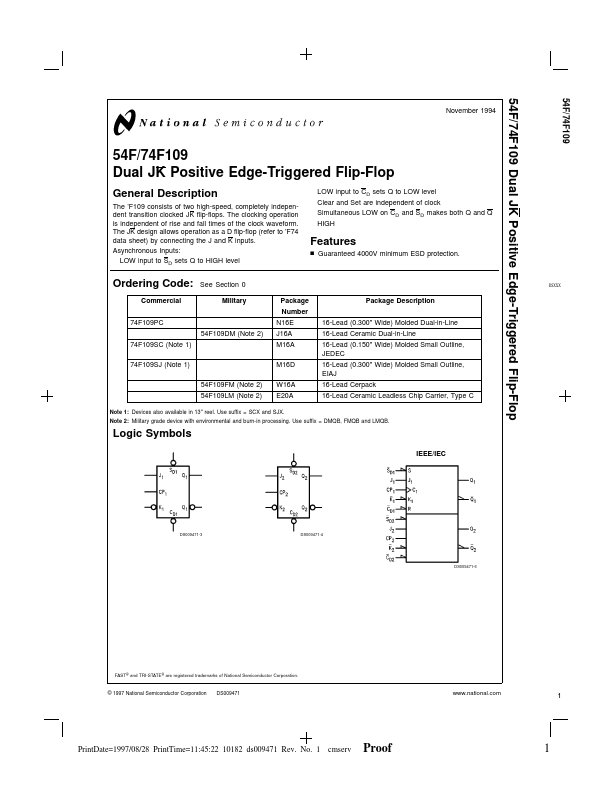

The ’F109 consists of two high-speed, pletely independent transition clocked JK flip-flops. The clocking operation is independent of rise and fall times of the clock waveform. The JK design allows operation as a D flip-flop (refer to ’F74 data sheet) by connecting the J and K inputs.

Asynchronous Inputs:

LOW input to SD sets Q to HIGH level

LOW input to CD sets Q to LOW level Clear and Set are independent of clock Simultaneous LOW on CD and SD makes both Q and Q HIGH

Features n Guaranteed 4000V minimum ESD protection.

Ordering Code: See Section 0 mercial

Military

74F109PC 74F109SC (Note 1)

54F109DM (Note 2)

74F109SJ (Note 1)

54F109FM (Note 2) 54F109LM (Note 2)

Package Number N16E J16A M16A

M16D

W16A E20A

Package Description

16-Lead (0.300" Wide) Molded Dual-in-Line 16-Lead Ceramic Dual-in-Line 16-Lead (0.150"...