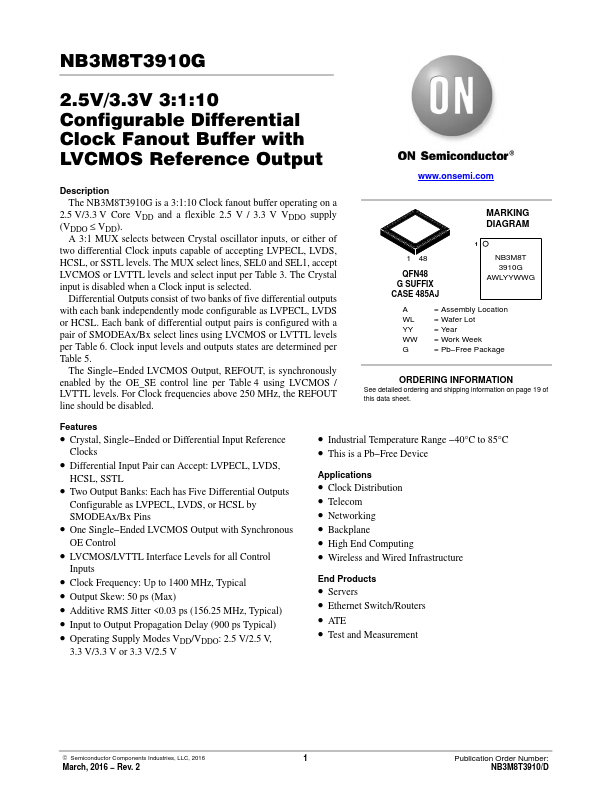

NB3M8T3910G

NB3M8T3910G is 2.5V/3.3V 3:1:10 Configurable Differential Clock Fanout Buffer manufactured by onsemi.

2.5V/3.3V 3:1:10 Configurable Differential Clock Fanout Buffer with LVCMOS Reference Output

Description The NB3M8T3910G is a 3:1:10 Clock fanout buffer operating on a

2.5 V/3.3 V Core VDD and a flexible 2.5 V / 3.3 V VDDO supply (VDDO ≤ VDD).

A 3:1 MUX selects between Crystal oscillator inputs, or either of two differential Clock inputs capable of accepting LVPECL, LVDS, HCSL, or SSTL levels. The MUX select lines, SEL0 and SEL1, accept LVCMOS or LVTTL levels and select input per Table 3. The Crystal input is disabled when a Clock input is selected.

Differential Outputs consist of two banks of five differential outputs with each bank independently mode configurable as LVPECL, LVDS or HCSL. Each bank of differential output pairs is configured with a pair of SMODEAx/Bx select lines using LVCMOS or LVTTL levels per Table 6. Clock input levels and outputs states are determined per Table 5.

The Single- Ended LVCMOS Output, REFOUT, is synchronously enabled by the OE_SE...