NB3N3001

NB3N3001 is PureEdge Clock Generator manufactured by onsemi.

..

3.3 V 106.25 MHz/ 212.5 MHz Pure Edge Clock Generator with LVPECL Differential Output

Description

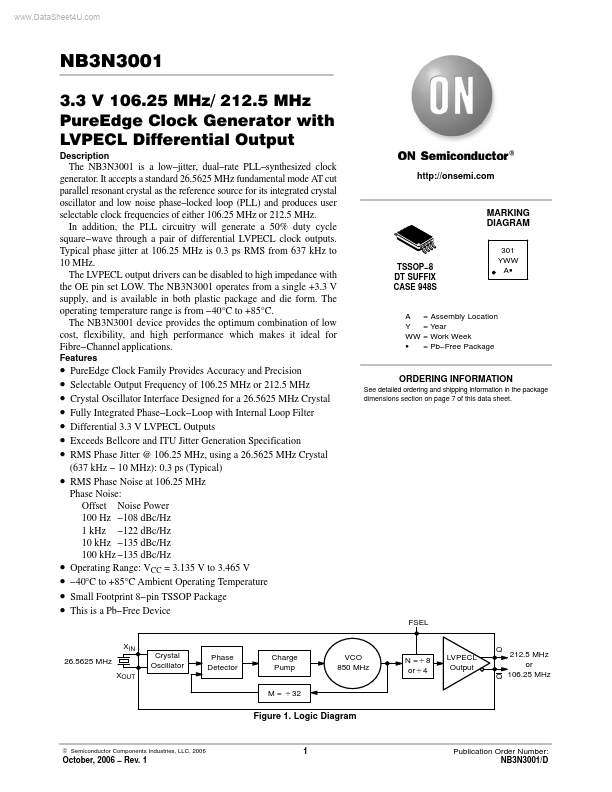

The NB3N3001 is a low- jitter, dual- rate PLL- synthesized clock generator. It accepts a standard 26.5625 MHz fundamental mode AT cut parallel resonant crystal as the reference source for its integrated crystal oscillator and low noise phase- locked loop (PLL) and produces user selectable clock frequencies of either 106.25 MHz or 212.5 MHz. In addition, the PLL circuitry will generate a 50% duty cycle square- wave through a pair of differential LVPECL clock outputs. Typical phase jitter at 106.25 MHz is 0.3 ps RMS from 637 k Hz to 10 MHz. The LVPECL output drivers can be disabled to high impedance with the OE pin set LOW. The NB3N3001 operates from a single +3.3 V supply, and is available in both plastic package and die form. The operating temperature range is from

- 40°C to +85°C. The NB3N3001 device provides the optimum bination of low cost, flexibility, and high performance which makes it ideal for Fibre- Channel applications.

Features http://onsemi.

MARKING DIAGRAM

301 YWW AG

TSSOP- 8 DT SUFFIX CASE 948S

A Y WW G

= Assembly Location = Year = Work Week = Pb- Free Package

- -

- -

- -

- -

- -

- -

Pure Edge Clock Family Provides Accuracy and Precision Selectable Output Frequency of 106.25 MHz or 212.5 MHz Crystal Oscillator Interface Designed for a 26.5625 MHz Crystal Fully Integrated Phase- Lock- Loop with Internal Loop Filter Differential 3.3 V LVPECL Outputs Exceeds Bellcore and ITU Jitter Generation Specification RMS Phase Jitter @ 106.25 MHz, using a 26.5625 MHz Crystal (637 k Hz

- 10 MHz): 0.3 ps (Typical) RMS Phase Noise at 106.25 MHz Phase Noise: Offset Noise Power 100 Hz

- 108 d Bc/Hz 1 k Hz

- 122 d Bc/Hz 10 k Hz

- 135 d Bc/Hz 100 k Hz

- 135 d Bc/Hz Operating Range: VCC = 3.135 V to 3.465 V

- 40°C to +85°C Ambient Operating Temperature Small Footprint 8- pin TSSOP Package This is a Pb- Free Device

ORDERING INFORMATION

See detailed ordering...