NB4N855S

NB4N855S is Dual AnyLevel to LVDS Receiver/Driver/Buffer/Translator manufactured by onsemi.

3.3 V, 1.5 Gb/s Dual

Any Level™ to LVDS Receiver/Driver/Buffer/ Translator

Description NB4N855S is a clock or data Receiver/Driver/Buffer/Translator capable of translating Any Level input signal (LVPECL, CML, HSTL, LVDS, or LVTTL/LVCMOS) to LVDS. Depending on the distance, noise immunity of the system design, and transmission line media, this device will receive, drive or translate data or clock signals up to 1.5 Gb/s or 1.0 GHz, respectively. This device is pin- for- pin plug in patible to the SY55855V in a 3.3 V applications.

The NB4N855S has a wide input mon mode range of GND + 50 m V to VCC

- 50 m V. This feature is ideal for translating differential or single- ended data or clock signals to 350 m V typical LVDS output levels.

The device is offered in a small 10 lead MSOP package. NB4N855S is targeted for data, wireless and tele applications as well as high speed logic interface where jitter and package size are main requirements.

Application notes, models, and support documentation are available at .onsemi..

Features

- Guaranteed Input Clock Frequency up to 1.0 GHz

- Guaranteed Input Data Rate up to 1.5 Gb/s

- 490 ps Maximum Propagation Delay

- 1.0 ps Maximum RMS Jitter

- 180 ps Maximum Rise/Fall Times

- Single Power Supply; VCC = 3.3 V ±10%

- Temperature pensated TIA/EIA- 644 pliant LVDS Outputs

- GND + 50 m V to VCC

- 50 m V VCMR Range

- This is a Pb- Free Device http://onsemi.

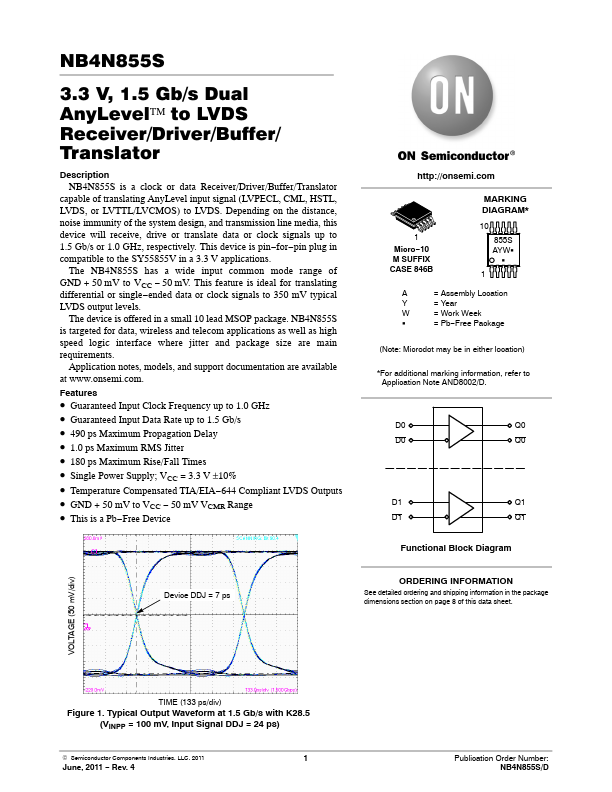

Micro- 10 M SUFFIX CASE 846B

MARKING DIAGRAM-

855S AYWG

A = Assembly Location Y = Year W = Work Week

G = Pb- Free Package

(Note: Microdot may be in either location)

- For additional marking information, refer to

Application Note AND8002/D.

D0 Q0 D0 Q0

D1 Q1 D1 Q1

Functional Block Diagram

Device DDJ = 7...