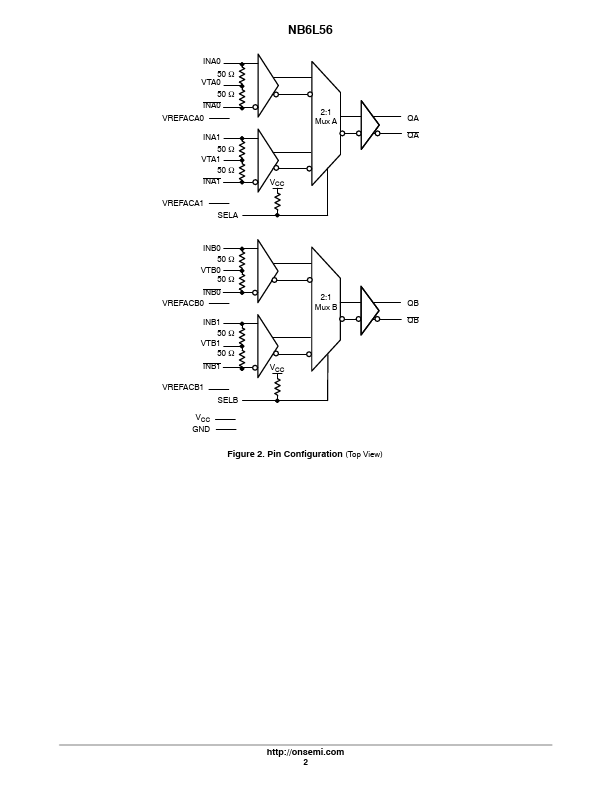

NB6L56 Description

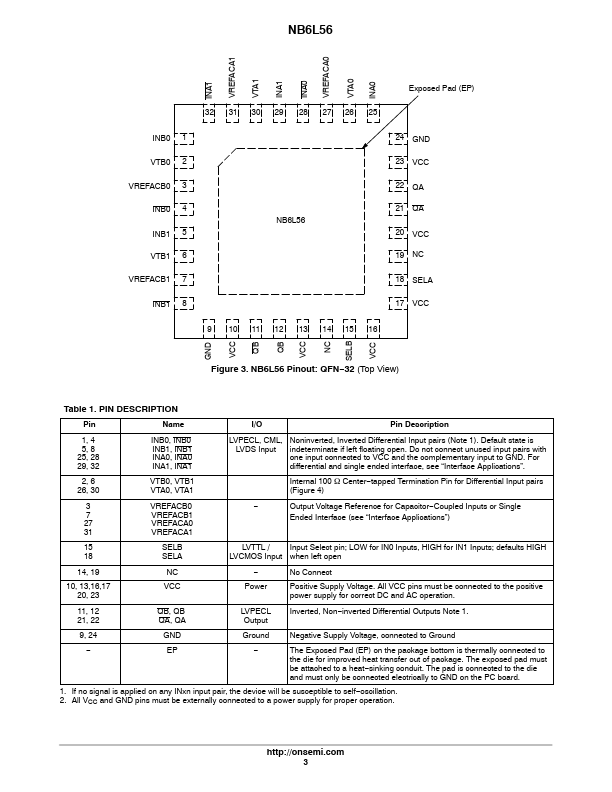

Pin Name I/O Pin Description 1, 4 5, 8 25, 28 29, 32 INB0, INB0 INB1, INB1 INA0, INA0 INA1, INA1 LVPECL, CML, LVDS Input Noninverted, Inverted Differential Input pairs (Note 1).

NB6L56 Key Features

- Maximum Input Data Rate > 2.5 Gbps

- Maximum Input Clock Frequency > 2.5 GHz

- Jitter

- 360 ps Max Propagation Delay

- 180 ps Max Rise and Fall Times

- Operating Range

- Internal 50 W Input Termination Resistors

- Industrial Temp. Range (-40°C to 85°C)

- QFN-32 Package

- These are Pb-Free Devices