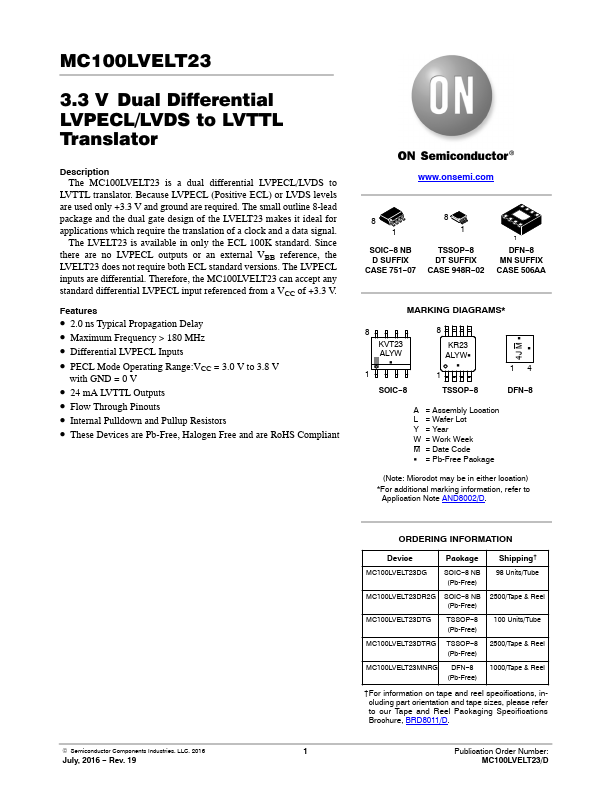

| Part | MC100LVELT23 |

|---|---|

| Description | Dual Differential LVPECL to TTL Translator |

| Manufacturer | onsemi |

| Size | 147.53 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC100LVELT23 | Motorola Semiconductor | DUAL DIFFERENTIAL LVPECL/LVDS TO LVTTL TRANSLATOR |

| MC100LVELT22 | Motorola Semiconductor | DUAL LVTTL/LVCMOS TO DIFFERENTIAL LVPECL TRANSLATOR |