PI6LC48S25A

PI6LC48S25A is Ethernet Network Clock Generator manufactured by Pericom Semiconductor.

Next Generation HiFlexTM Ethernet Network Clock Generator

Features

ÎÎ3.3V & 2.5V supply voltage ÎÎCrystal/CMOS input: 25 MHz ÎÎDifferential input: 25MHz, 125MHz, and 156.25 MHz ÎÎOutput frequencies: 312.5, 156.25, 125, 100, 50, 25MHz ÎÎ4 Output banks with selectable output signaling: LVPECL or

LVDS ÎÎLow 0.3ps typical integrated phase noise design: 156.25MHz

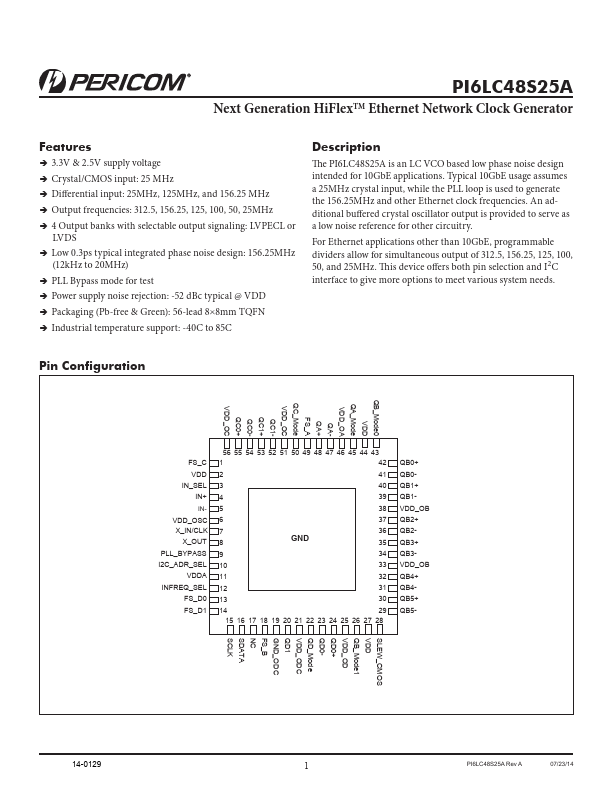

(12kHz to 20MHz) ÎÎPLL Bypass mode for test ÎÎPower supply noise rejection: -52 dBc typical @ VDD ÎÎPackaging (Pb-free & Green): 56-lead 8×8mm TQFN ÎÎIndustrial temperature support: -40C to 85C

Description

The PI6LC48S25A is an LC VCO based low phase noise design intended for 10GbE applications. Typical 10GbE usage...