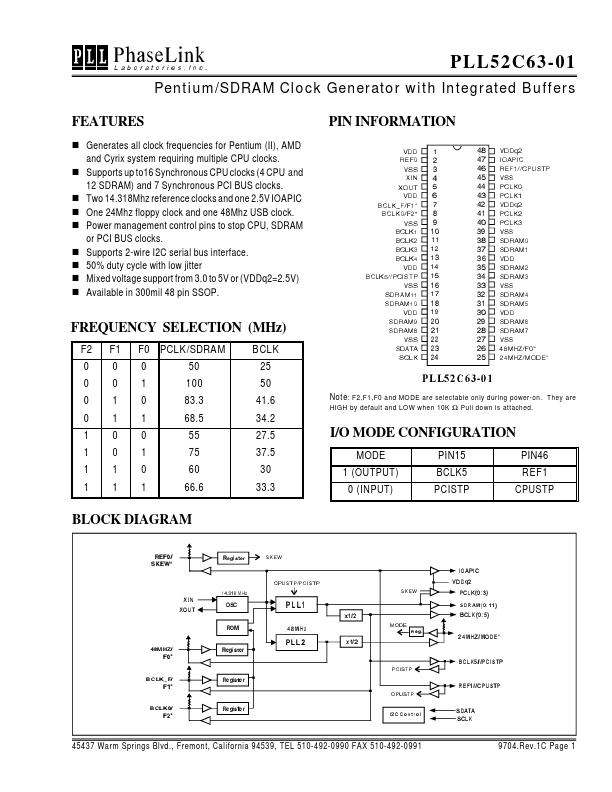

PLL52C63-01 Overview

Key Features

- Supports up to16 Synchronous CPU clocks (4 CPU and 12 SDRAM) and 7 Synchronous PCI BUS clocks

- Two 14.318Mhz reference clocks and one 2.5V IOAPIC

- One 24Mhz floppy clock and one 48Mhz USB clock

- Power management control pins to stop CPU, SDRAM or PCI BUS clocks

- Supports 2-wire I2C serial bus interface. n 50% duty cycle with low jitter