853S057

Description

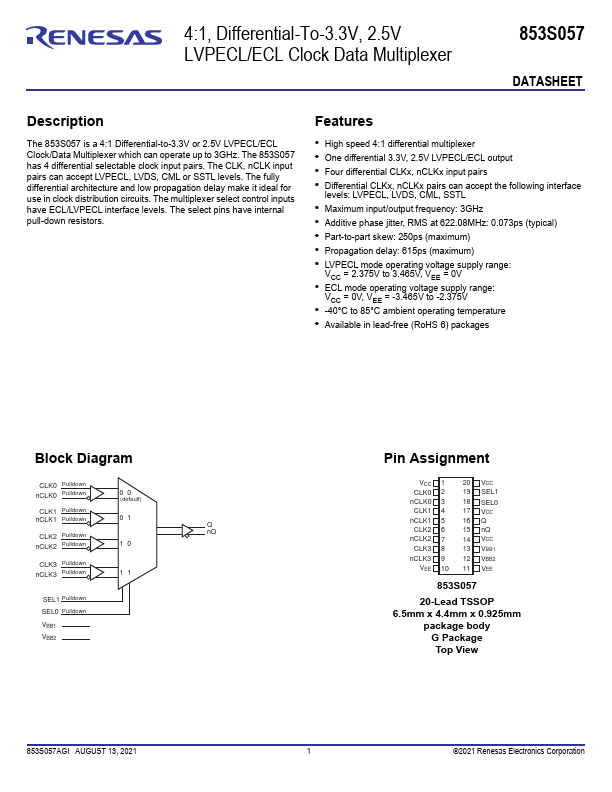

The 853S057 is a 4:1 Differential-to-3.3V or 2.5V LVPECL/ECL Clock/Data Multiplexer which can operate up to 3GHz.

Key Features

- High speed 4:1 differential multiplexer

- One differential 3.3V, 2.5V LVPECL/ECL output

- Four differential CLKx, nCLKx input pairs

- Differential CLKx, nCLKx pairs can accept the following interface levels: LVPECL, LVDS, CML, SSTL

- Maximum input/output frequency: 3GHz

- Additive phase jitter, RMS at 622.08MHz: 0.073ps (typical)

- Part-to-part skew: 250ps (maximum)

- Propagation delay: 615ps (maximum)

- LVPECL mode operating voltage supply range: VCC = 2.375V to 3.465V, VEE = 0V

- ECL mode operating voltage supply range: VCC = 0V, VEE = -3.465V to -2.375V