ICS95V847

ICS95V847 is Clock Driver manufactured by Renesas.

ICS95V8 47

2.5V Wide Range Frequency Clock Driver (45MHz

- 233MHz)

Remended Application:

- Zero Delay Board Fan Out, SO-DIMM

- Provides plete DDR registered DIMM solution with ICSSSTV16857, ICSSSTV16859 or ICSSSTV32852

Product Description/Features

:

- Low skew, low jitter PLL clock driver

- 1 to 5 differential clock distribution (SSTL_2)

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

Switching Characteristics:

- CYCLE

- CYCLE jitter: <60ps

- OUTPUT

- OUTPUT skew: <60ps

- Period jitter: ±30ps

- DUTY CYCLE: 49.5%

- 50.5%

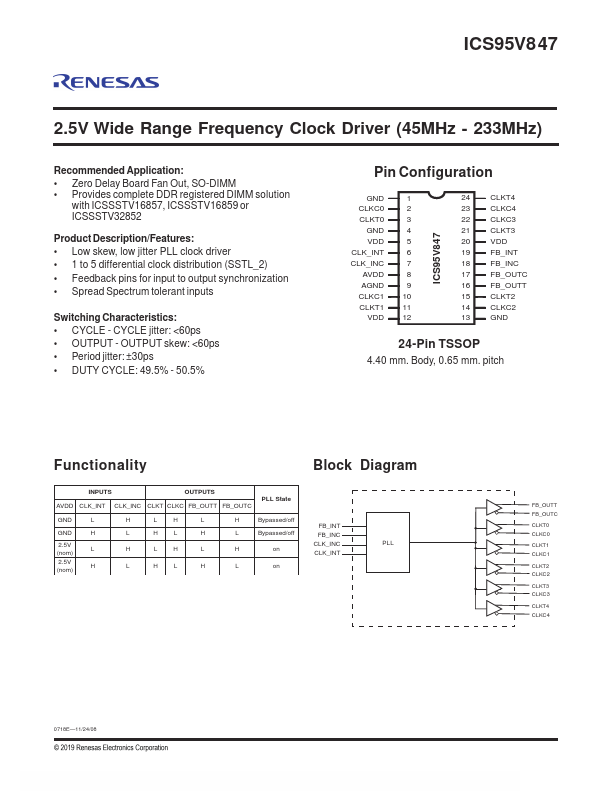

Pin Configuration

GND CLKC0 CLKT0

GND VDD CLK_INT CLK_INC AVDD AGND CLKC1 CLKT1 VDD

1 2 3 4 5 6 7 8 9 10 11...