ISLA224S

ISLA224S is High Speed Serial Output ADC manufactured by Renesas.

features including the fine gain and offset adjustments of the two ADC cores as well as the programmable clock divider, enabling 2x and 4x harmonic clocking.

The ISLA224S is available in a space-saving 7mmx7mm 48 Ld QFN package. The package features a thermal pad for improved thermal performance and is specified over the full industrial temperature range (-40°C to +85°C).

Features

- JESD204A/B High Speed Data Interface

- JESD204A pliant

- JESD204B Device Subclass 0 pliant

- JESD204B Device Subclass 2 patible

- Up to 3 JESD204 Output Lanes Running up to 4.375Gbps

- Highly Configurable JESD204 Transmitter

- Multiple Chip Time Alignment and Deterministic Latency Support (JESD204B Device Subclass 2)

- SPI Programmable Debugging Features and Test Patterns

- 48-pin QFN 7mmx7mm Package

Key Specifications

- SNR @ 250/200/125MSPS 73.2/74.1/75.1 d BFS f IN = 30MHz 72.4/72.9/73.2 d BFS f IN = 190MHz

- SFDR @ 250/200/125MSPS 82/91/94 d Bc f IN = 30MHz 84/82/81 d Bc f IN = 190MHz

- Total Power Consumption: 989m W @ 250MSPS

Applications

- Radar and Satellite Antenna Array Processing

- Broadband munications and Microwave Receivers

- High-Performance Data Acquisition

- munications Test Equipment

- High-Speed Medical Imaging

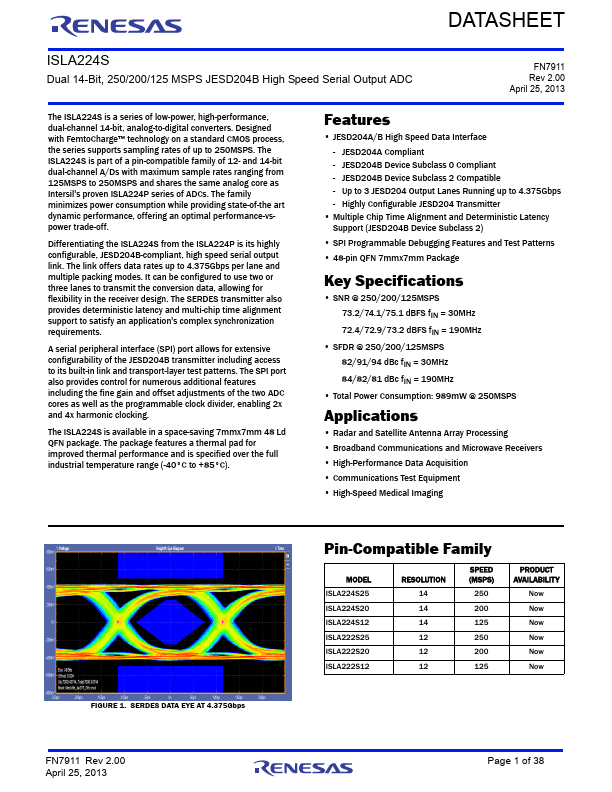

FIGURE 1. SERDES DATA EYE AT 4.375Gbps

Pin-patible Family

MODEL ISLA224S25 ISLA224S20 ISLA224S12 ISLA222S25 ISLA222S20 ISLA222S12

RESOLUTION 14 14 14 12 12 12

SPEED (MSPS)

250 200 125 250 200 125

PRODUCT AVAILABILITY

Now Now Now Now Now Now

FN7911 Rev 2.00 April 25, 2013

Page 1 of 38

AVDD...