M68Z512

M68Z512 is 4 Mbit 512Kb x8 Low Power SRAM with Output Enable manufactured by STMicroelectronics.

DESCRIPTION

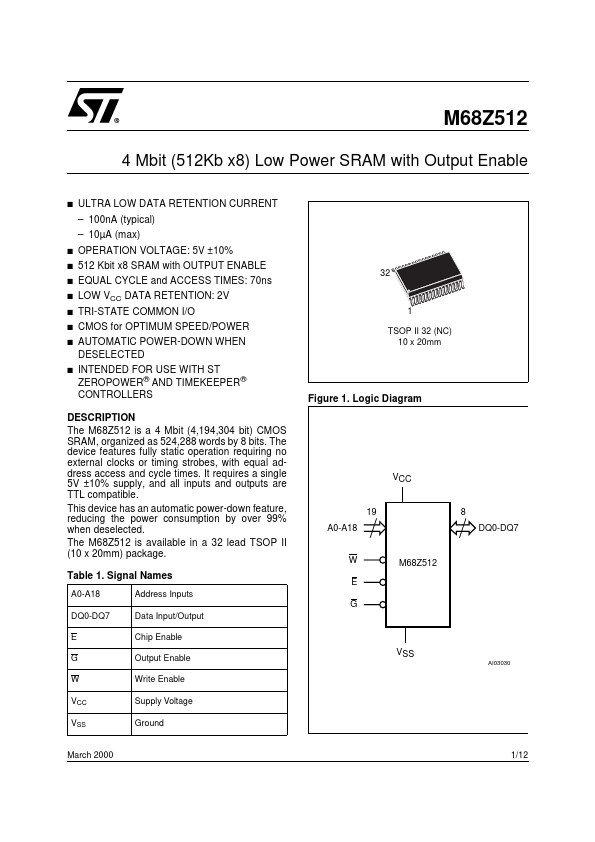

The M68Z512 is a 4 Mbit (4,194,304 bit) CMOS SRAM, organized as 524,288 words by 8 bits. The device features fully static operation requiring no external clocks or timing strobes, with equal address access and cycle times. It requires a single 5V ±10% supply, and all inputs and outputs are TTL patible. This device has an automatic power-down feature

, reducing the power consumption by over 99% when deselected. The M68Z512 is available in a 32 lead TSOP II (10 x 20mm) package. Table 1. Signal Names

A0-A18 DQ0-DQ7 E G W VCC VSS Address Inputs

19 A0-A18

8 DQ0-DQ7

Data Input/Output Chip Enable Output Enable Write Enable Supply Voltage Ground

AI03030

March 2000

1/12

Table 2. Absolute Maximum Ratings (1)

Symbol TA TSTG VIO (2) VCC IO (3) PD Parameter Ambient Operating Temperature Storage Temperature Input or Output Voltage Supply Voltage Output Current Power Dissipation Value 0 to 70

- 65 to 150

- 0.3 to VCC + 0.3

- 0.3 to 7.0 20 1 Unit °C °C V V m A W

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents. 2. Up to a maximum operating VCC of 5.5V only. 3. One output at a time, not to exceed 1 second duration.

Figure 2. TSOP Connections

A17 A16 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 DQ0 DQ1 DQ2 VSS

8 9

25 24

AI03031

VCC A15 A18 W A13 A8 A9 A11 G A10 E DQ7 DQ6 DQ5 DQ4 DQ3

READ MODE The M68Z512 is in the Read mode whenever Write Enable (W) is High with Output Enable (G) Low, and Chip Enable (E) is asserted. This provides access to...