M74HC113

M74HC113 is DUAL J-K FLIP FLOP WITH PRESET manufactured by STMicroelectronics.

M54HC113 M74HC113

DUAL J-K FLIP FLOP WITH PRESET

- . . .

HIGH SPEED f MAX = 71 MHz (TYP.) at VCC = 5 V LOW POWER DISSIPATION ICC = 2 µA at TA = 25 °C HIGH NOISE IMMUNITY VNIH = VNIL = 28 % VCC (MIN.) OUTPUT DRIVE CAPABILITY 10 LSTTL LOADS SYMMETRICAL OUTPUT IMPEDANCE |IOH| = IOL = 4 m A (MIN.) BALANCED PROPAGATION DELAYS t PLH = t PHL WIDE OPERATING VOLTAGE RANGE VCC (OPR) = 2 V to 6 V PIN AND FUNCTION PATIBLE WITH 54/74LS113

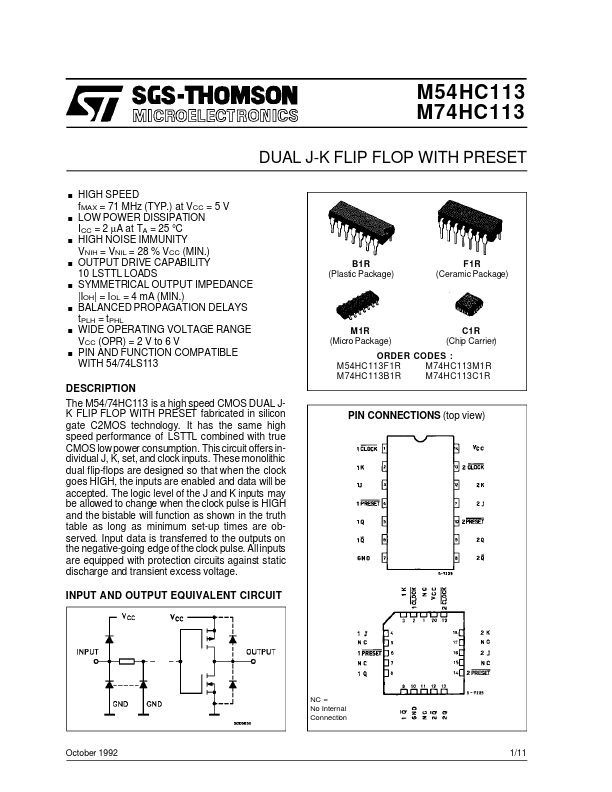

B1R (Plastic Package)

F1R (Ceramic Package)

M1R (Micro Package)

C1R (Chip Carrier)

ORDER CODES : M54HC113F1R M74HC113M1R M74HC113B1R M74HC113C1R

DESCRIPTION The M54/74HC113 is a high speed CMOS DUAL JK FLIP FLOP WITH PRESET fabricated in silicon gate C2MOS technology. It has the same high speed performance of LSTTL bined with true CMOS low power consumption. This circuit offers individual J, K, set, and clock inputs. These monolithic dual flip-flops are designed so that when the clock goes HIGH, the inputs are enabled and data will be accepted. The logic level of the J and K inputs may be allowed to change when the clock pulse is HIGH and the bistable will function as shown in the truth table as long as minimum set-up times are observed. Input data is transferred to the outputs on the negative-going edge of the clock pulse. All inputs are equipped with protection circuits against static discharge and transient excess voltage. INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN CONNECTIONS (top view)

NC = No Internal Connection

October 1992

1/11

M54/M74HC113

TRUTH TABLE

INPUTS PR L H H H H H

X: Don’t Care

OUTPUTS K X L H L H X CK X Q H Qn L H Qn Qn Q L Qn H L Qn Qn

J X L L H H X

FUNCTION PRESET NO CHANGE

TOGGLE NO CHANGE

LOGIC DIAGRAM

2/11

M54/M74HC113

PIN DESCRIPTION

PIN No 1, 13 2, 12 3, 11 4, 10 5, 9 6, 8 7 14 SYMBOL 1CK, 2CK 1K, 2K 1J, 2J 1PR, 2PR 1Q, 2Q 1Q, 2Q GND V CC NAME AND FUNCTION Clock Input (HIGH to LOW edge triggered) Data Inputs: Flip-Flop 1 and 2 Data Inputs: Flip-Flop 1 and 2 Set Inputs True Flip-Flop Outputs...