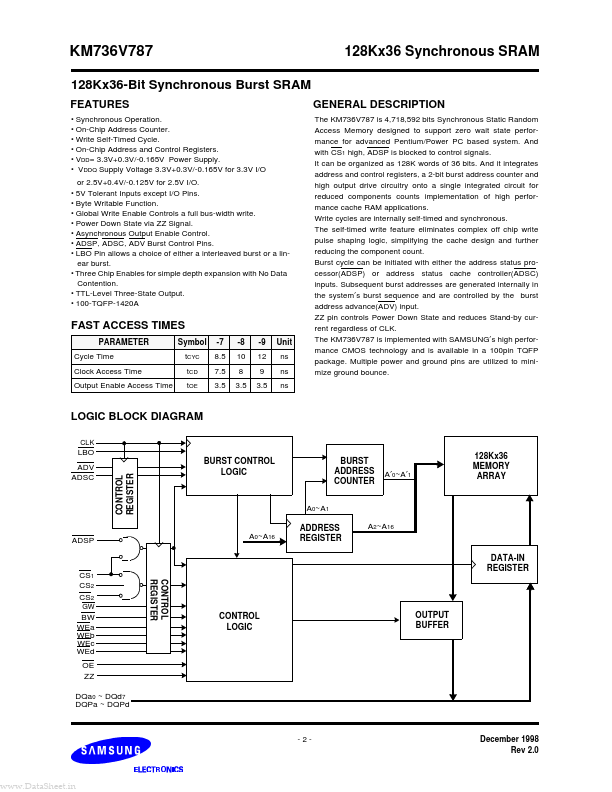

KM736V787 Description

The KM736V787 is 4,718,592 bits Synchronous Static Random Access Memory designed to support zero wait state performance for advanced Pentium/Power PC based system. And with CS1 high, ADSP is blocked to control signals. It can be organized as 128K words of 36 bits.

KM736V787 Key Features

- Synchronous Operation

- On-Chip Address Counter

- Write Self-Timed Cycle

- On-Chip Address and Control Registers

- VDD= 3.3V+0.3V/-0.165V Power Supply

- 5V Tolerant Inputs except I/O Pins

- Byte Writable Function

- Global Write Enable Controls a full bus-width write

- Power Down State via ZZ Signal

- Asynchronous Output Enable Control