K7Q161882A Description

Changed at x36 organization. Reserved pin for high density name change from NC to Vss/SA 1. Modify Draft Date May, 22 2001 Remark Advance Sep,03 2001 Advance 0.2 Nov.

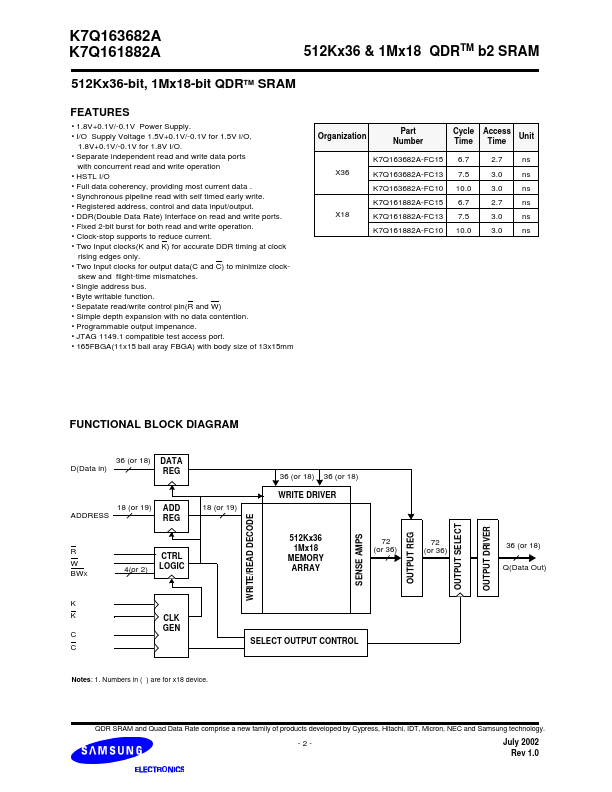

K7Q161882A Key Features

- 1.8V+0.1V/-0.1V Power Supply

- I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O, 1.8V+0.1V/-0.1V for 1.8V I/O

- Separate independent read and write data ports with concurrent read and write operation

- HSTL I/O

- Full data coherency, providing most current data

- Synchronous pipeline read with self timed early write

- Registered address, control and data input/output

- DDR(Double Data Rate) Interface on read and write ports

- Fixed 2-bit burst for both read and write operation

- Clock-stop supports to reduce current