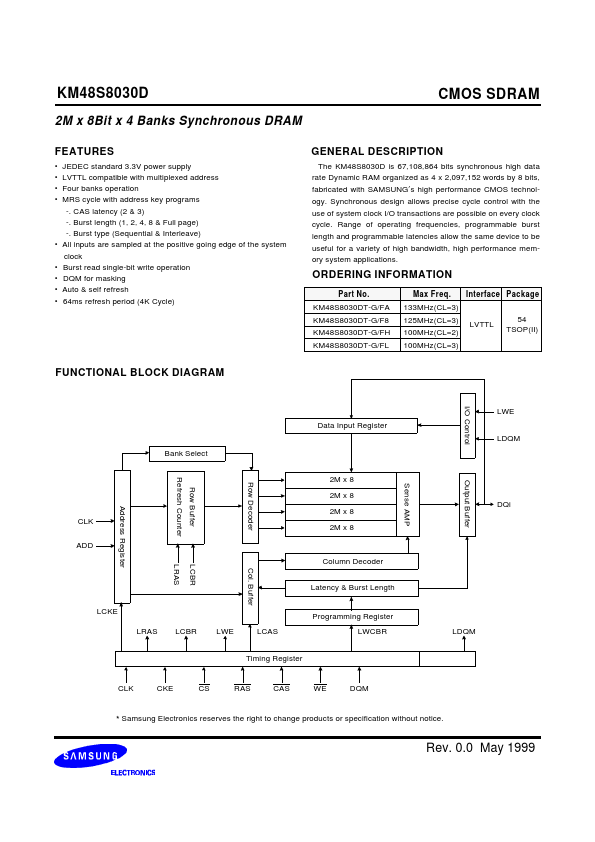

KM48S8030D Description

The KM48S8030D is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 8 bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be...