KM681001A

KM681001A is 128K x 8 Bit High-Speed CMOS Static RAM manufactured by Samsung Semiconductor.

PRELIMINARY

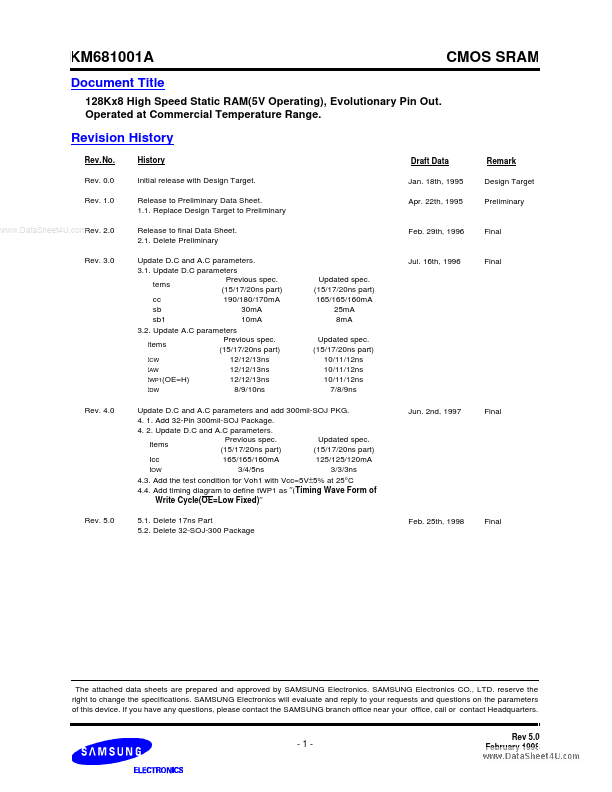

Document Title

128Kx8 High Speed Static RAM(5V Operating), Evolutionary Pin Out. Operated at mercial Temperature Range.

CMOS SRAM

Revision History

Rev. No. Rev. 0.0 Rev. 1.0 History Initial release with Design Target. Release to Preliminary Data Sheet. 1.1. Replace Design Target to Preliminary Release to final Data Sheet. 2.1. Delete Preliminary Update D.C and A.C parameters. 3.1. Update D.C parameters Previous spec. Items (15/17/20ns part) Icc 190/180/170m A Isb 30m A Isb1 10m A 3.2. Update A.C parameters Previous spec. Items (15/17/20ns part) t CW 12/12/13ns t AW 12/12/13ns t WP1(OE=H) 12/12/13ns t DW 8/9/10ns Draft Data Jan. 18th, 1995 Apr. 22th, 1995 Remark Design Target Preliminary

.. Rev. 2.0

Feb. 29th, 1996

Final

Rev. 3.0

Jul. 16th, 1996 Updated spec. (15/17/20ns part) 165/165/160m A 25m A 8m A Updated spec. (15/17/20ns part) 10/11/12ns 10/11/12ns 10/11/12ns 7/8/9ns Jun. 2nd, 1997

Final

Rev. 4.0

Update D.C and A.C parameters and add 300mil-SOJ PKG. 4. 1. Add 32-Pin 300mil-SOJ Package. 4. 2. Update D.C and A.C parameters. Previous spec. Updated spec. Items (15/17/20ns part) (15/17/20ns part) Icc 165/165/160m A 125/125/120m A t OW 3/4/5ns 3/3/3ns 4.3. Add the test condition for Voh1 with Vcc=5V±5% at 25°C 4.4. Add timing diagram to define t WP1 as ″(Timing Wave Form of Write Cycle(OE=Low Fixed)″ 5.1. Delete 17ns Part 5.2. Delete 32-SOJ-300 Package

Final

Rev. 5.0

Feb. 25th, 1998

Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any questions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

-1-

Rev 5.0 February 1998

PRELIMINARY

128K x 8 Bit High-Speed CMOS Static RAM

Features

- Fast Access Time 15, 20ns(Max.)

- Low Power Dissipation Standby...