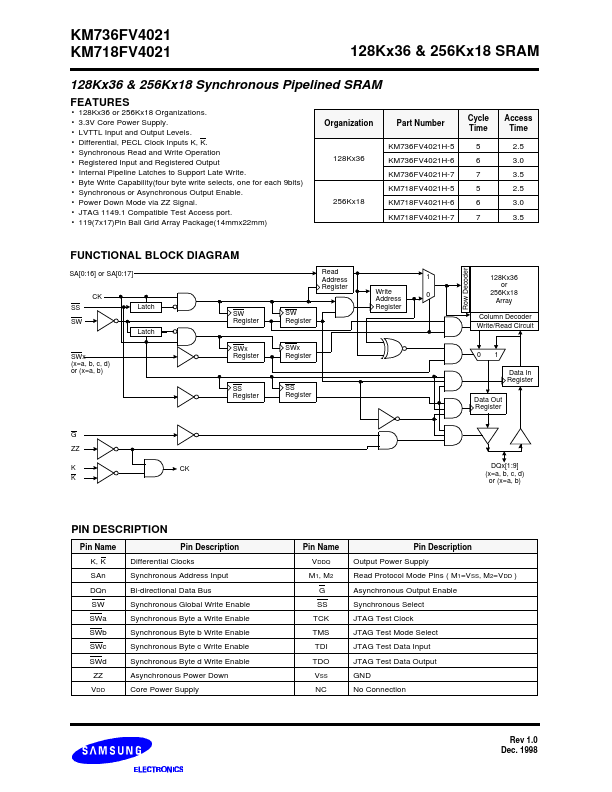

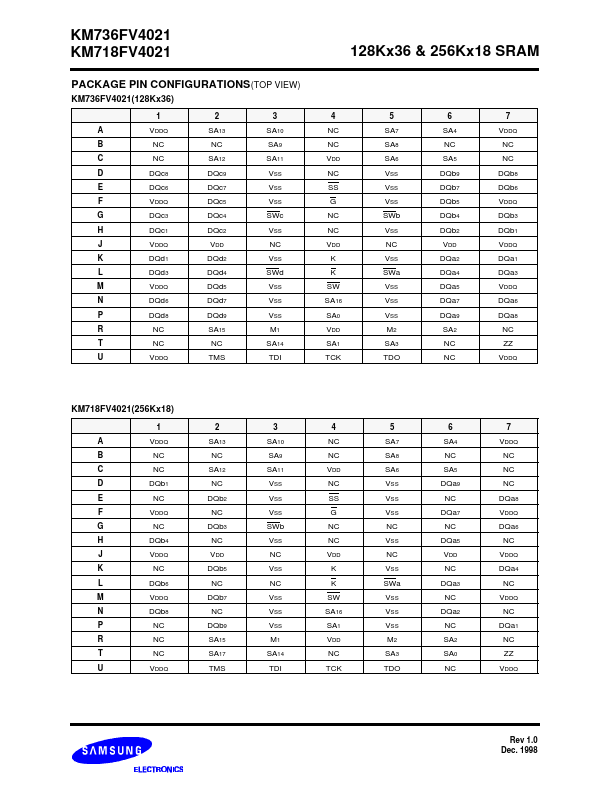

- Part: KM736FV4021

- Description: 128Kx36 & 256Kx18 Synchronous Pipelined SRAM

- Manufacturer: Samsung Semiconductor

- Size: 350.04 KB

Related Samsung Semiconductor Datasheets

| Part Number | Description |

|---|---|

| KM736V687 | 64Kx36-Bit Synchronous Burst SRAM |

| KM736V687A | 64Kx36-Bit Synchronous Burst SRAM |

| KM736V689 | 64Kx36-Bit Synchronous Pipelined Burst SRAM |

| KM736V689A | 64Kx36-Bit Synchronous Pipelined Burst SRAM |

| KM736V747 | 128Kx36 & 256Kx18 Flow-Through NtRAM |