SK10E116

SK10E116 is Quint Differential Line Receiver manufactured by SEMTECH.

SK10/100E116

HIGH-PER.ORMANCE PRODUCTS Description

The SK10/100E116 is a quint differential line receiver designed for use in new, high-performance ECL systems. The receiver design Features clamp circuitry to cause a defined output state if both the inverting and non-inverting inputs are left open; in this case the Q output goes low, while the Q- output goes high. This feature makes the device ideal for twisted pair applications. If both inverting and non-inverting inputs are at an equal potential of >- 2.9V, the receiver does not go to a defined state, but rather shares current in normal differential amplifier fashion, producing output voltage levels midway between high and low. This may even cause the device to oscillate. The SK10/100E116 provides VBB output for either singleended use or as a DC bias for AC coupling to the device. The VBB output pin should be used only as a DC bias for the E116 as its current sink/source capability is limited. Whenever used, the VBB pin should be bypassed to VCC via a 0.01 µF capacitor.

Quint Differential Line Receiver

.eatures

- -

- -

- -

- - 500 ps Maximum Propagation Delay Extended VEE Range of

- 4.2V to

- 5.5V VBB Output for Single-Ended Reception Internal 75KΩ Input Pull-Down Resistors ESD Protection of >4000V Fully patible with MC10E/100E116 Specified Over Industrial Temperature Range:

- 40o C to +85o C Available in 28-Pin PLCC Package

PIN Description

Pin D0, D0- D4, D4- Q0, Q0- -Q4, Q4- VBB VCC0 .unction Differential Input Pairs Differential Output Pairs Reference Voltage Output VCC to Output

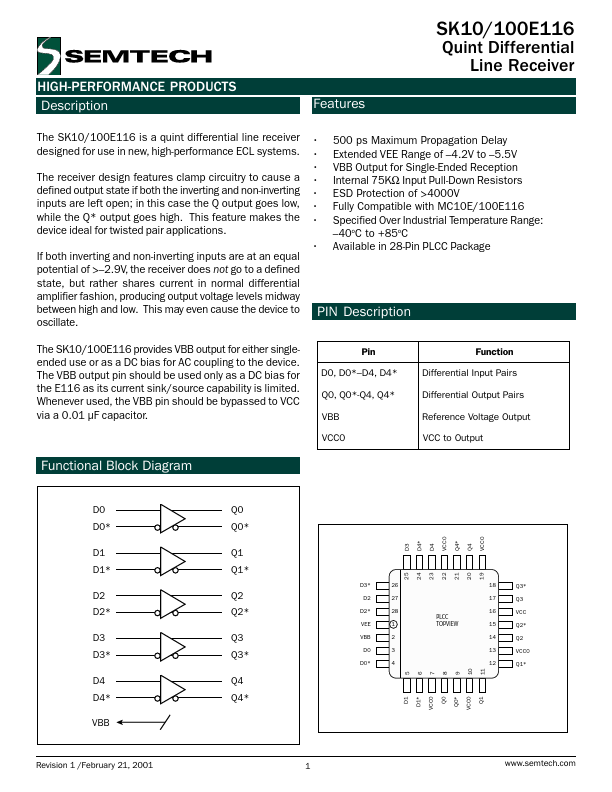

.unctional Block Diagram

D0 D0- D1 D1- D2 D2- D3 D3- D4 D4- VBB Q0 Q0-

VCC0 VCC0 19

D4-

Q4- 21

D3

D4

Q1 Q1-

D3- 26 27 28 1 2 3 4

Q4

18 17 16 PLCC TOPVIEW 15 14 13 12

10 11 5 6 7 8 9

Q3- Q3 VCC Q2- Q2 VCC0 Q1-

Q2 Q2- Q3 Q3- Q4

D2 D2- VEE VBB D0 D0-...