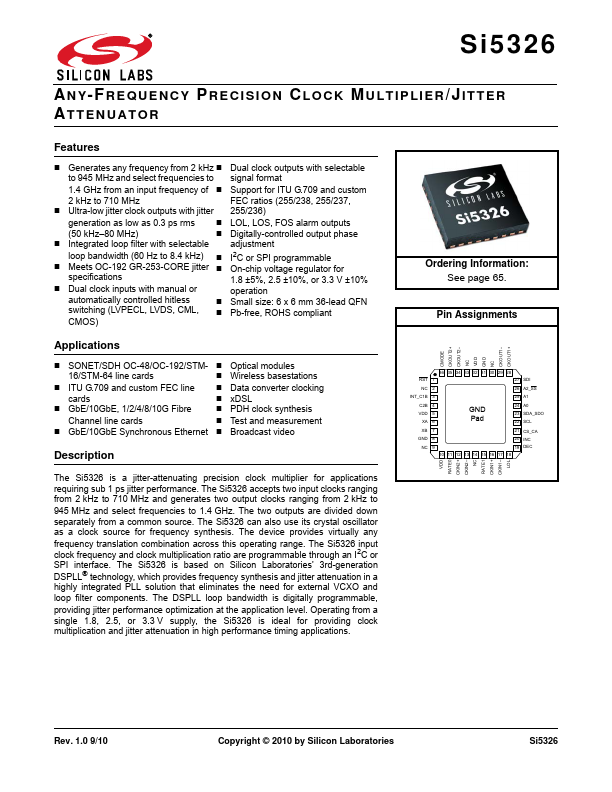

SI5326 Overview

Key Specifications

Operating Voltage: 1.8 V

Max Voltage (typical range): 1.89 V

Min Voltage (typical range): 1.71 V

Length: 6 mm

Description

The Si5326 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance. The Si5326 accepts two input clocks ranging from 2 kHz to 710 MHz and generates two output clocks ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz.

Key Features

- Generates any frequency from 2 kHz

- Dual clock outputs with selectable to 945 MHz and select frequencies to signal format 1.4 GHz from an input frequency of

- Support for ITU G.709 and custom 2 kHz to 710 MHz FEC ratios (255/238, 255/237

- Ultra-low jitter clock outputs with jitter 255/236) generation as low as 0.3 ps rms

- LOL, LOS, FOS alarm outputs (50 kHz–80 MHz)