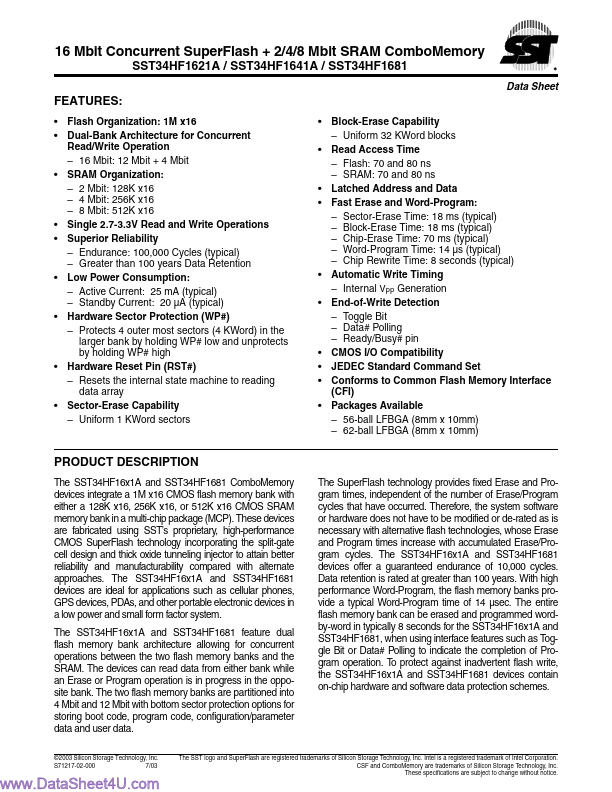

SST34HF1641A Overview

Key Features

- Flash Organization: 1M x16

- Dual-Bank Architecture for Concurrent Read/Write Operation – 16 Mbit: 12 Mbit + 4 Mbit

- SRAM Organization: – 2 Mbit: 128K x16 – 4 Mbit: 256K x16 – 8 Mbit: 512K x16

- Single 2.7-3.3V Read and Write Operations

- Superior Reliability – Endurance: 100,000 Cycles (typical) – Greater than 100 years Data Retention

- Low Power Consumption: – Active Current: 25 mA (typical) – Standby Current: 20 µA (typical)

- Hardware Reset Pin (RST#) – Resets the internal state machine to reading data array

- Sector-Erase Capability – Uniform 1 KWord sectors

- Block-Erase Capability – Uniform 32 KWord blocks

- Read Access Time – Flash: 70 and 80 ns – SRAM: 70 and 80 ns