CXK77P18E160GB

CXK77P18E160GB is 16Mb LW R-L HSTL High Speed Synchronous SRAMs (512K x 36 or 1M x 18) manufactured by Sony Semiconductor Solutions.

- Part of the CXK comparator family.

- Part of the CXK comparator family.

SONY®

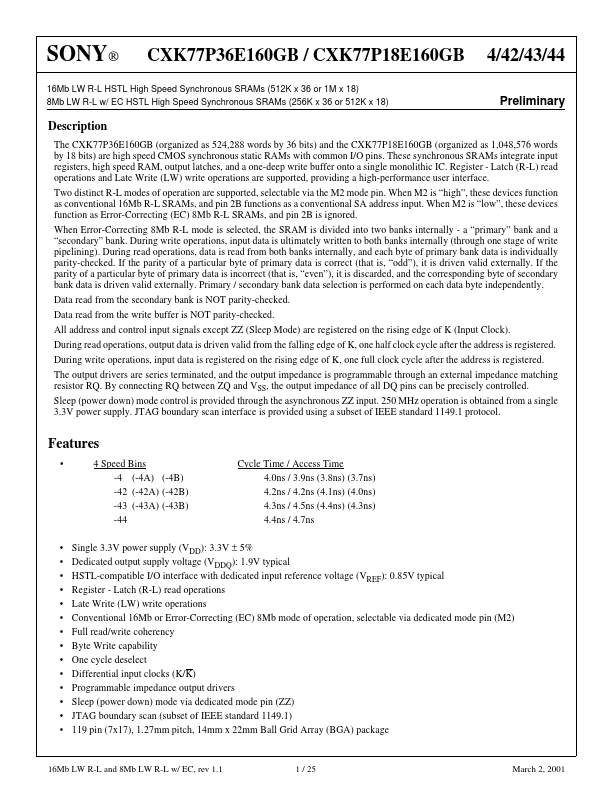

CXK77P36E160GB / CXK77P18E160GB

4/42/43/44

Preliminary

16Mb LW R-L HSTL High Speed Synchronous SRAMs (512K x 36 or 1M x 18) 8Mb LW R-L w/ EC HSTL High Speed Synchronous SRAMs (256K x 36 or 512K x 18)

Description

The CXK77P36E160GB (organized as 524,288 words by 36 bits) and the CXK77P18E160GB (organized as 1,048,576 words by 18 bits) are high speed CMOS synchronous static RAMs with mon I/O pins. These synchronous SRAMs integrate input registers, high speed RAM, output latches, and a one-deep write buffer onto a single monolithic IC. Register

- Latch (R-L) read operations and Late Write (LW) write operations are supported, providing a high-performance user interface. Two distinct R-L modes of operation are supported, selectable via the M2 mode pin. When M2 is “high”, these devices function as conventional 16Mb R-L SRAMs, and pin 2B functions as a conventional SA address input. When M2 is “low”, these devices function as Error-Correcting (EC) 8Mb R-L SRAMs, and pin 2B is ignored. When Error-Correcting 8Mb R-L mode is selected, the SRAM is divided into two banks internally

- a “primary” bank and a “secondary” bank. During write operations, input data is ultimately written to both banks internally (through one stage of write pipelining). During read operations, data is read from both banks internally, and each byte of primary bank data is individually parity-checked. If the parity of a particular byte of primary data is correct (that is, “odd”), it is driven valid externally. If the parity of a particular byte of primary data is incorrect (that is, “even”), it is discarded, and the corresponding byte of secondary bank data is driven valid externally. Primary / secondary bank data selection is performed on each data byte independently. Data read from the secondary bank is NOT parity-checked. Data read from the write buffer is NOT parity-checked. All address and control input signals except ZZ (Sleep Mode) are registered on the rising edge of K (Input...